# Stable High-Speed Digital-to-Analog Conversion for Storage Tube Deflection

By C. F. AULT

(Manuscript received October 30, 1958)

This paper covers the design of access circuitry for a barrier grid tube temporary memory. The circuitry converts a 14-bit binary address into the analog deflection voltage necessary to deflect the electron beam in the barrier grid tube to a specific geometrical storage area defined by the address.

A special feedback circuit and raster reference tube deflected in parallel with the barrier grid tube control the size and centering of the array of storage spots. Novel methods of measurement were developed to certify the accuracy of the deflection system.

The system meets the requirements of high speed, accuracy, stability and reliability.

#### I. INTRODUCTION

A barrier grid tube is a specialized cathode ray tube developed for high-speed electrostatic storage. Instead of a phosphor screen which changes the electron beam into visible light, there is a target area which stores isolated regions of charge under beam action. A binary "1" is recorded by charging a small target area ("spot") to equilibrium with the beam when the target surface is modulated by a back plate voltage pulse, while a "0" is stored by charging a spot to equilibrium in the absence of the back plate voltage pulse. Information is "read out" the next time the beam is turned on a spot (in the absence of a back plate pulse), the "1" giving a large output until the spot reaches equilibrium.

The barrier grid store, which is a random-access, single-bit, binary memory, utilizes the barrier grid tube as the storage device. To function properly, the store must have a deflection system which converts a binary address to an analog voltage that deflects the barrier grid tube beam to a unique physical storage location. A barrier grid store<sup>1</sup> and a

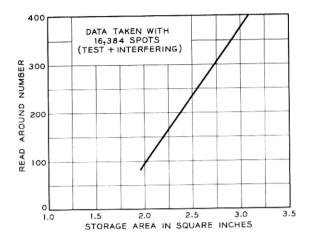

Fig. 1 — Effect on Read Around Number (RAN) of variations in spacing.

barrier grid tube<sup>2</sup> have been described in previous issues of the Bell System Technical Journal.

The deflection requirements for a particular barrier grid store are derived primarily from the capabilities of the barrier grid tube and secondarily from system requirements governing allowable time for regeneration of stored information in the memory. The spacing between stored charges and the total number of charges determine the interference resulting from operations on adjacent and distant spots, and hence determine the system time required for regeneration.

The effect of changing the spacing between storage centers on the interference due to reading and writing on other storage spots is illustrated in Fig. 1. The measure of interference used is the number of times the spots adjacent to a particular or test spot may be operated on before the storage of the test spot is degraded below usable levels. The actual measurement is made by writing a double-spaced checkboard of test spots over the storage area and then writing m frames of interfering spots in the skipped spaces. Each frame is counted as a "Read Around Number" (RAN) of four, since each test spot has four adjacent interfering spots. A 10 per cent decrease in the size of the storage area decreases the RAN by 50 per cent.

Minimum cost per storage location can only be achieved by utilizing the tube storage area to the fullest extent, commensurate with satisfactory immunity from interference and economical use of access or deflection circuitry. The more efficient access circuit schemes utilize a binary address of 2n bits, which will define an n vertical by n horizontal

square array of  $2^{2n}$  discrete storage sites. However, the storage area of the barrier grid tube currently used is circular, and a circle with an inscribed square has about one third its area outside the square. It is not always possible to deflect the beam to the edge of the storage area without its first hitting a deflection plate; consequently, the area outside the inscribed square that can be safely used requires extra addressing circuitry, which the additional number of storage sites may not justify. If necessary, some of this outside area could be used. The best access compromise appears to be a square binary array with just enough separation between spots to yield the required freedom from interference.

The binary-to-analog conversion system discussed in this paper produces an array of 128 × 128, or 16,384 spots. The spot spacing is sufficient to guarantee a RAN of 150. This RAN is maintained by utilizing the inscribed storage area to the fullest extent, so that no appreciable guard space is allowed to absorb any drift of the deflection system. This was accomplished by designing a servo (raster reference system to be described later) which holds the storage array in a fixed geometrical location

#### II. DESIGN CONSIDERATIONS

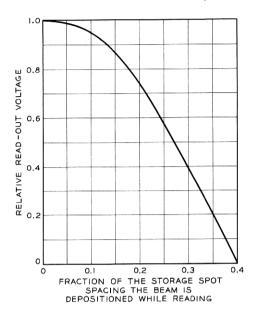

A deflection system must have a method for remembering the address of the latest storage location received and a method for converting the address to the correct deflection voltage. To these primary considerations are added those of speed, accuracy, power and reliability. These are not separate problems; a decision about one affects all the others. The energy available at the output of the barrier grid tube is at a maximum if the beam is repositioned exactly where it was at the time of writing. Fig. 2 is a plot showing how the read out signal decreases as the beam is moved off the initial storage location. From this figure, it is apparent that the beam center can be 20 per cent of the beam diameter off the spot without the voltage output being significantly decreased. The beam diameter may only be one-half to one-third as large as the spot spacing. This means, for a 128 × 128 array, an accuracy of deflection better than 0.1 per cent.

It takes a fixed amount of time to read and write information in a barrier grid tube. The tube for which this development was intended required 0.75 microsecond to be read and 0.75 microsecond to be written. A reasonable time for deflection would be one that would not increase the cycle time more than 30 to 50 per cent. The deflection time should not be made any faster than necessary, because the amount of power used for deflection increases with speed.

Fig. 2 — Degradation of barrier grid tube output voltage occurring when the beam is repositioned for reading off of the center of the stored charge.

The cycle time for a store consists of (a) time for deflection, (b) time for reading, (c) time for writing and (d) time for writing transients to decay. Item (d) does not increase the cycle time if the transients are present only during the following deflection. However, if they should last into the following reading time, they might cause errors in the read out. If the transients last longer than the deflection time, no decrease in cycle time could be obtained from a decrease in deflection time. Before reading could commence, the start of the next cycle would have to wait until all transients had decayed sufficiently to permit complete recovery.

#### III. DESIGN OBJECTIVES

The deflection system developed for the barrier grid store was allowed 0.3 microsecond to settle. The balance of the 2.5-microsecond period (system objective) is 0.1 microsecond for jitter of order pulses with respect to address pulses, 0.75 microsecond for reading, 0.75 microsecond for writing and 0.1 microsecond for turning off the beam. The rest of the period, 0.6 microsecond, is used for transient recovery. The deflection time is not as long as the recovery time because it is desirable to have the readout from the barrier grid store available to the central

control of the electronic switching system as soon as possible after the order pulses are received.

The deflection objective of 0.3 microsecond may seem quite modest until the required accuracy is considered. An RC circuit will settle to 0.1 per cent in about seven times the time constant. The 10 to 90 per cent rise time of this deflection voltage then must be better than 0.09 microsecond. The rise time (10 to 90 per cent) of most amplifiers equals 2.2 RC:

$$7(\text{time constant}) = 0.3 \ \mu\text{s},$$

$$\text{time constant} = \frac{0.3 \ \mu\text{s}}{7},$$

$$\text{rise time } (10\text{--}90\%) = 2.2 \times \left(\frac{0.3 \ \mu\text{s}}{7}\right) = 0.09 \ \mu\text{s}.$$

The total tolerance for deflection cannot be allowed for settling, because there is some noise coupled to the deflection plates from other pulse circuits in the store. The design objective was therefore set at 0.05 microsecond rise time.

The deflection circuit used in the barrier grid store satisfies the following requirements:

- i. The push-pull output of 140 volts is sufficient to deflect the tube over a square raster inscribed in the circular target of the tube. Push-pull deflection is necessary to prevent a change in average voltage for a pair of deflection plates which would defocus the beam.

- ii. The output of 70 volts per deflection plate is developed across 72  $\mu\mu$ f in 0.05 microsecond. The capacity is divided: tube plus wiring, 40  $\mu\mu$ f; amplifier, 32  $\mu\mu$ f. To develop this output requires an average current of 100 ma.

- iii. The voltage to one deflection plate should be the complement of that to the other, so that capacitive coupling to the target by one plate will be cancelled by the capacitive coupling from the other plate.

- iv. The average voltage per pair of deflection plates is 0 volts. The average voltage of a pair of plates has to be at ground potential because, if it is different from the target voltage, defocusing occurs. It was found to be impractical to run the target at other than ground potential because of the increased recovery time of transients due to the back plate drive. With the deflection voltage at ground potential, the coupling of the deflection voltage to the raster reference tube (described in Section V), dynamic focus circuit and deflection monitor is facilitated.

#### IV. SYSTEM DESIGN

With the requirements for deflection defined, a comparison can now be made of various ways to satisfy them. The methods considered fall into two general categories, which are generally referred to as "highlevel" and "low-level" conversion.

A low-level system converts the digital address to a proportional current or voltage at a small value and then amplifies this low value to the correct voltage necessary to deflect the barrier grid tube. A high-level conversion system converts the address to a voltage which is large enough to deflect the tube without amplification.

If an electronic switch is available which is good enough to meet the exacting requirements of a high-level system, it is probably the preferred method of deflection, even though it might use more power than a low-level system would.

A low-level system also requires a good switch, but this switch need only control low currents with small voltage swings. Electron tube diodes such as the 6AL5 and some of the newer silicon diodes are satisfactory for this application. At high currents the electron tubes have too much and too variable a voltage drop, and at high voltages the silicon diodes fail.

## 4.1 High-Level System

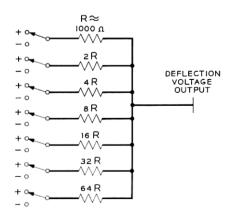

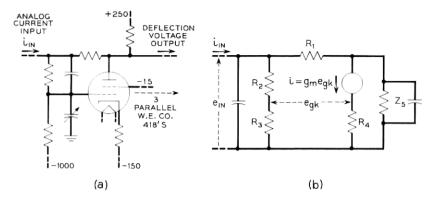

Fig. 3 is a schematic of a particular type of high-level decoder. The output has to be at ground potential, so equal positive and negative voltages are used. A switch for each digit connects a resistor to the plus

Fig. 3 — High-level digital-to-analog conversion.

voltage for a "1" address and to the minus voltage for a "0" address. The resistors determine the correct current for each digit, thereby controlling the spacing between storage spots; the magnitude of the plus and minus voltages determines the size of the array. For a 0.05-microsecond rise time, R must equal 1000 ohms; V=35 volts, so the current through the switch of the msd (most significant digit) varies from zero to 35 ma. The stiffest requirement on the switches occurs for the msd. When the switches are closed, the voltage across each must be constant with time and temperature to 0.1 volt. The switch may have some resistance, since R may be decreased to compensate for it. The switch must be able to withstand 70 volts and open and close in less than 0.05 microsecond.

### 4.2 Low-Level System

Fig. 4 is a schematic of a particular low-level system. There are three major divisions: (a) an input register for remembering the address, (b) a digital-to-analog converter to change the register output to an analog current and (c) an amplifier to change the analog current into the deflection voltage.

Fig. 4 — Low-level deflection.

The input register consists of flip-flops which produce a larger current than any digit current in the D-A (digital-to-analog) converter. The voltage swing of the output of the flip-flops must be greater than the largest digit current multiplied by the diode resistance, plus twice the largest digit current times the input impedance of the amplifier. When the flip-flop output voltage swing is larger than necessary, it is reduced to prevent excessive capacity coupling through the diodes. Both the rise and fall time must be faster than the 10–90 per cent rise time required of the deflection system or else it will limit the speed.

The D-A converter converts the digital output of the flip-flops to the correct current for the digit it represents. The practical limit for a D-A converter, at speeds of 0.05 microsecond and accuracies of a tenth of a spot, is about eight digits. This limit is certainly true using vacuum tube diodes, whereas by using some of the new silicon diodes possibly nine digits might be switched. To switch nine digits the maximum current possible should be switched by the msd. A reasonable current for this might be 30 ma. The flip-flop must then be able to produce 30 ma. No problem will be encountered using this current through the diode, but the current into the amplifier is rather high, so that the feedback resistor will have to handle four or five watts, which is objectionable. The average current through the amplifier load resistor will have to be increased by an amount equal to the current in the feedback resistor.

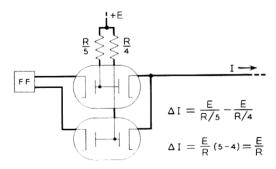

If the msd current is 30 ma, the least significant digit current must be 30 ma divided by 28, or about 120 microamperes. If the drop across the diodes is 1 volt and the input impedance of the amplifier at high frequencies is 100 ohms, the flip-flop voltage swing must be greater than 7 volts. Assuming a 10-volt swing, a current of 120  $\mu$ a must charge any distributed capacity associated with a diode and the resistor supplying the 120  $\mu$ a. The capacity is not less than 2  $\mu\mu$ f, so the rise time of this diode for the 10 volts it must charge through before any current flows is 0.17 microsecond. The next digit will take 0.085 microsecond, which is still marginal. To speed up these two slow digits and to make them less subject to noise, a system of adding and subtracting currents that makes it possible to switch reasonable currents may be adopted. The diode switch is connected as shown in Fig. 5. To produce a one-unit increase in current at the output, five units of current are added and four units are subtracted. It is important not to switch currents any larger than necessary, because any drift of the resistor tolerance is multiplied by the amount by which the current exceeds the difference in currents.

Solid state diode recovery time specifications are usually to 90 per

cent recovery from an initial forward current. Some of these, in which this 90 per cent time is 0.01 microsecond, are satisfactory for this application. Since the time of recovery after the 90 per cent time is not usually specified or controlled, some care must be exercised in their use. Some fast silicon diodes have long current decay times from 10 per cent to zero. The diodes with short decay times generally have larger initial current flow when switching occurs than do the diodes with long decay times.

When vacuum tube diodes are used, it is useful to limit the current to about 4 ma through any one diode. If more current is needed, another diode is used. If too much current is used, the diode voltage drop becomes large and the voltage across the current determining resistors must be increased. If too low a voltage is used across the current-determining resistors, the output per unit digit change decreases as more digits feed current into the amplifier. If the amplifier input voltage changes 2 volts and the voltage across the resistor is 100 volts, then the input current decreases 2 per cent. A 2 per cent change in input current causes a change in voltage across the feedback resistor of 0.8 volts. This results in an increase in average voltage for a pair of deflection plates and causes slight defocusing at the edges. If the input impedance of the amplifier were higher or the D-A current higher, this shift in average voltage could cause excessive defocusing.

A brief review of the amplifier requirements for a low-level system may help at this point:

- i. Input and output approximately at 0 volts average per pair.

- ii. Current necessary to charge and discharge 70  $\mu\mu$ f 70 volts in 0.05 microsecond is 100 ma.

- iii. Low input impedance necessary to sum digital-to-analog current output correctly.

Fig. 5 — Low-level digital-to-analog converter — least significant digit.

Fig. 6 — (a) Deflection amplifier and (b) equivalent circuit for determining input impednace.

iv. Low output impedance necessary to be immune to interfering capacitively-coupled noise.

v. Must be all dc coupled or else have the direct current reinserted by some means such as a clamp.

The low-level digital-to-analog conversion easily meets the requirements for seven binary digits. The amplifier requirements are also reasonable, so the low-level system was chosen over the high-level system.

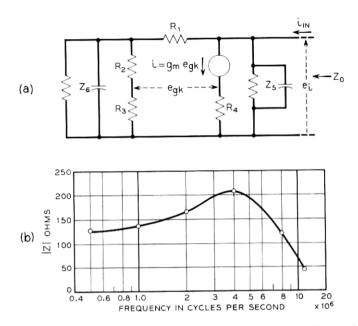

Fig. 6(a) is a simplified schematic of the deflection amplifier circuit chosen for use in the barrier grid store developed for the electronic switching system. Fig. 6(b) is the simplified equivalent circuit with the approximate component values. The input impedance (Appendix A) is 73 ohms at low frequencies. At higher frequencies the loop gain decreases, because the impedance of  $z_{5}$  (output load resistor in parallel with distributed capacity) decreases, causing the input impedance to increase. At still higher frequencies, the input impedance decreases because of the distributed capacity at the input.

Fig. 7(a) gives the equivalent circuit for determining the output impedance. The calculated output impedance (Appendix B) is 34 ohms at low frequencies. At higher frequencies, the output impedance increases, as in Fig. 7(b). At still higher frequencies, the impedance decreases because of the capacitive component of  $z_{\rm 5}$ .

The design of this particular amplifier had to fit within the power supply voltages compatible with and necessary to the rest of the store. The voltages and tubes available permit a design not usually practical. The tubes, Western Electric Company type 418, have a very high GM (25,750) and a figure of merit such that only one stage of amplification

Fig. 7 — (a) Equivalent circuit for determining output impedance of deflection amplifier and (b) measured output impedance.

was necessary to attain the rise time and low input and output impedances desired. Even the requirement that the input and output be at ground potential average was not a handicap, because -1000 volts was available for the voltage divider from the input to the grids, which permits a shift of 150 volts between the input and the grids, with a loss of only 15 per cent of the input voltage.

The average current through  $R_{\rm 5}$ , the plate load resistor, is 100 ma. To handle this current conservatively requires three tubes in parallel. To minimize the screen dissipation, the screens are run at -15 volts with respect to ground potential or 135 volts with respect to the cathode. The three tubes were chosen over one tube with larger power-dissipating capabilities because of the resulting very high composite transconductance. If one large tube had been used it would have necessitated an extra stage of amplification, thus complicating the design considerably. Cathode degeneration is employed to equalize the currents through each of the three tubes.

One problem encountered at the junction of the cathodes of the six push-pull tubes was making this point stay at a constant voltage. Any change in voltage at this point can make the deflection very inaccurate. The problem was solved by building a regulator on each deflection amplifier chassis that compares the cathode voltage to a reference obtained from the -1000-volt supply. The regulator holds the voltage constant from 0 to several hundred cycles, after which the capacitors take over.

#### V. RASTER REFERENCE

The optimum condition for storage in a barrier grid tube occurs when the array of spots (raster) is centered so that each corner spot is the same distance from the edge of the barrier grid storage surface as are the other three corner spots. This distance should be as small as possible, so as to avoid crowding the other spots and thereby reducing the RAN. A reduction in spacing of even one spot has a measurable effect on RAN.

However, the deflection amplifier will drift and the voltage from the different power supplies will change with time. The power supplies have a definite drift limit, beyond which an automatic voltage-monitoring system in the electronic switching system would sound an alarm. If a guard band were left between the storage array and the edge of the barrier grid assembly by shrinking the size of the raster, drift of the supplies could be accommodated. Each axis would decrease in length by 1 per cent. If the voltages now change so as to decrease the size of the array it may end up with each axis 2 per cent shorter. A similar guard band must be left to compensate for drift of the amplifier and of the power supply voltage used for centering the array. This could amount to a 2 per cent decrease at each end or a 4 per cent decrease in length of each axis. It is almost impossible to set these tolerances in practice with any great accuracy, so a workable guard band might be about an 8 per cent decrease in length of each axis. This guard band is sufficient to reduce the RAN by almost 50 per cent.

A special raster reference system was developed to control the position of the array, thereby permitting the reductions of this guard band from 8 per cent to less than 1 per cent.

The flying spot store<sup>3</sup> has a servo which controls the position of the beam at every address. This complex circuitry can only be justified for very large amounts of storage. The raster reference system used in the barrier grid store is a compromise system where only the edges of the array are controlled and the addresses in between the extremes depend on the stability of the digital-to-analog converter to maintain the correct spacing. Since a converter may drift, an increase in spacing for each digit is allowed. Each digit is about 101 per cent larger than

the preceding digit, which amounts to each axis being about 4 per cent shorter in effective length.

An ideal reference for the raster in a barrier grid tube would be one where the reference was inside the tube. This is difficult to accomplish, however, so the next best thing is to use a tube operated in parallel with the barrier grid tube which uses the same acceleration voltage and has similar conditions in general.

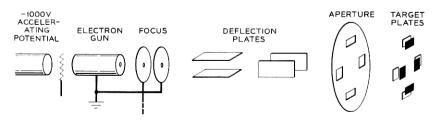

Fig. 8 is a drawing of the raster reference tube. At one end is an electron gun similar to that of the barrier grid tube, in the middle are two pairs of deflection plates and at the end are four pairs of overlapping plates, each with a knife edge at the overlapping edge nearest the gun. The edges are located in the position equivalent to the center of each edge of the array in the barrier grid tube.

In the electronic switching system the barrier grid store is regularly addressed to the center of one of the sides of the array and a pulse is sent to the store identifying the edge corresponding to the address. The address is not changed for the next 7.5 microseconds (three normal periods).

The raster reference tube beam will normally strike the knife edge, half of the current going to one of the pair of plates and half to the other. The plates have a secondary emission ratio which gives a current gain of about two. If there is an error in the position of the beam, one plate goes more positive than the other.

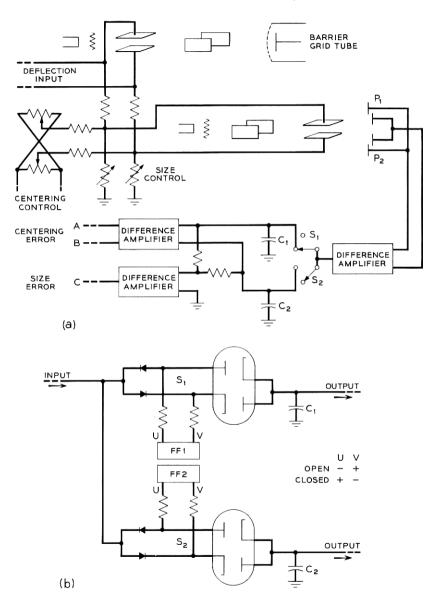

Fig. 9 is a simplified drawing of the raster reference tube circuitry. Approximately every 2.5 milliseconds the store is addressed to one of the pairs of plates in the raster reference tube. The error signal derived from each visit is stored in a capacitor. (There is a capacitor for each pair of plates.) From the voltages on the two capacitors from a particular axis, a centering and a size correction is generated.

If the barrier grid and the raster reference tubes all had the same sensitivity and centering they could be deflected in parallel by simply connecting each raster reference tube deflection plate to the correspond-

Fig. 8 — Raster reference tube.

Fig. 9 — (a) Raster reference system circuitry, with (b) flip-flop switches in detail.

ing plate of the barrier grid tube. Since they are not alike, some means must be provided for adjusting the deflection of the reference tube. To facilitate this adjustment, the reference tube was designed with twice the sensitivity of the barrier grid tube and a dividing network was placed between the tubes. This network is not compensated, because the reference is not required to settle as fast as the barrier grid tube, since the error output from the reference tube is the result of the average output for 7.5 microseconds.

The dividing network provides resistance between the tubes, across which a centering voltage is developed. The centering voltage is the algebraic difference in centering voltages of the two tubes. The current through the resistors used for centering must be held very constant, because any change in it causes the raster on the barrier grid tube to be decentered. The two tubes now in use have centering errors that require a 0.5 per cent accurate voltage supply to hold the centering to about half a spot. The centering output of the raster reference system is a differential current fed to the differential inputs to the deflection amplifier. The size output is the voltage used in the digital-to-analog converter, which determines the current for each digit.

The pairs of target plates in the raster reference tube are connected together in two groups, the outside plates making one group and the inside plates another. The operation of the raster reference system can test be explained if an error in position is assumed, either in centering or size.

Assume first an error in centering, with a deflection voltage drift so as to move the raster toward  $P_1$  (Fig. 9). Whenever the beam is on  $P_1$ ,  $S_1$  connects to  $C_1$  and will, in this case, charge it to a negative voltage because more of the beam hits the outer target than hits the inner target. When the beam is at  $P_2$ , the beam is mostly on the inner target and the switch connects to  $C_2$ , which is charged positive. The size amplifier output equals  $K_1(VC_1 + VC_2)$ . The centering amplifier equals  $K_2(VC_1 - VC_2)$ . When there is drift,  $VC_1 = -VC_2$ ; therefore, the centering output is  $2K_2 VC_1$  and the size output is zero.

If there is a size error but no drift, the size is too small, the beam hits the innermost plates at both  $\mathbf{p}_1$  and  $\mathbf{p}_2$ , both capacitors  $\mathbf{c}_1$  and  $\mathbf{c}_2$  are charged positive, and  $VC_1 = VC_2$ . The centering output in this case is zero and the size output is  $2K_1 \ VC_1$ . For either drift or size errors, the output of the raster reference system is in a direction to minimize the error.

The switches [Fig. 9(b)] are opened and closed by flip-flops, which are controlled by the central control portion of the electronic switching

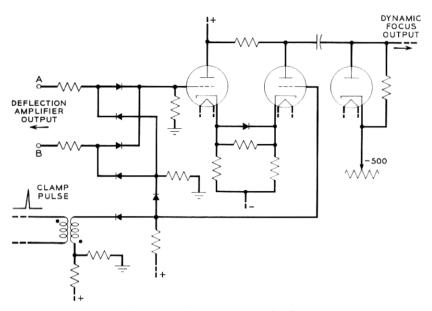

Fig. 10 - Dynamic focus circuit.

Fig. 11 — Dynamic focus voltage waveforms: (a) deflection voltage or dynamic focus input voltage; (b) dynamic focus output voltage.

system. When closed, a switch permits the circuitry to either charge or discharge the capacitors. Solid state diodes are used for one side of the switch because of their low forward impedance, and vacuum tube diodes are used for the other side because of their high back impedance. It is important that the charge not leak off the capacitor because the switch supplies current for only 7 microseconds and leakage drains the charge for 10 milliseconds.

The raster reference system is a sampled-data servo system where the sampling rate per axis is once every 10 milliseconds. Gain crossover for the loop must be below 50 cycles. There is no reason why the raster reference system has to be fast, so no effort was made to push the response to the limit. The open-loop gain depends on the beam current of the reference tube and the secondary emission ratio of the targets, consequently the break frequency has to be low enough so that the system is stable for any possible raster reference tube.

To make certain that noise in the raster reference circuitry does not cause errors in deflection, the integrating network was placed as near the output of the size and centering correction voltages as possible. The only tubes beyond the integrating network are cathode followers. The size output is single-ended, so that it is particularly susceptible to noise transients. A tetrode cathode follower is used whose screen voltage is carefully filtered.

The sampling rate and the duration of the sampling time were selected so as to fit simply into the electronic switching system<sup>4</sup> method of operation and still hold the array in place for reasonably fast changes in power supply voltages or other circuit drifts.

To a small extent, some of the circuitry that could have been built into the barrier grid store was replaced by the program stored in the flying spot store. The program tells the raster reference system when and at what address to operate. The servoing could have been accomplished without the help of a stored program but at a considerable increase in circuitry.

#### VI. DYNAMIC FOCUS

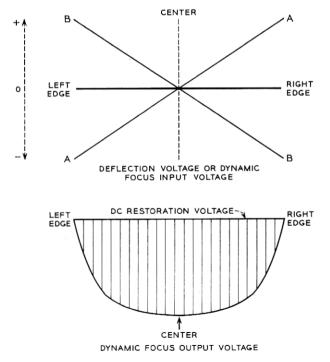

The operation of the present barrier grid tubes is improved if the beam is refocused when deflected near the edge of the raster. The beam-focusing voltage must be adjusted at each address before the beam is turned on. The dynamic focus circuit derives its input from the output of the deflection amplifier (Fig. 10). Fig. 11(a) is a plot of the output voltage of the deflection amplifier for one axis as the beam moves from one side of the tube to the other. Fig. 11(b) is a plot of the required output of the dynamic focus circuit.

The maximum dynamic focus voltage change occurs when the beam goes from the center to either edge. The correction may be as large as 20 volts, with a correction voltage being developed for each axis and applied to a corresponding dynamic focus electrode. The dynamic focus electrode is at approximately -500 volts. It would be difficult to couple the correction voltage from ground potential, where it is generated, to the correction electrode with dc coupling. To make it possible to avoid dc coupling, the correction voltage has a reference inserted at the time the orders are received. The reference is the most positive the correction will ever be, so it is possible to capacitively couple the correction from ground potential to the dynamic focus electrode at -500 volts and there use a diode to reinsert the dc level.

#### VII. METHOD OF MEASUREMENT

The required deflection accuracy is better than 0.1 per cent, and determining just how well a deflection circuit is performing is a difficult task. The deflection circuit is under the most strain when the deflection is from one edge to the other. Then, a 70-volt step must be measured to better than 0.1 per cent from 0.3 microsecond after the initial change to several seconds later. Three methods of measurement have been used to determine deflection accuracy.

The first method tried was to apply the deflection output to the plates of an oscilloscope. When the deflection voltage is a maximum, the area of interest is off the screen, so it was necessary to add a dc voltage in each lead between the deflection amplifier and the deflection plates. This voltage was positive in one lead, negative in the other. By taking successive photographs of the deflection voltage at one-spot increments, the accuracy of deflection could be seen to be within 0.1 spot at 0.3 microsecond.

The second method made use of the raster reference tube. The test equipment which supplied orders and addresses to the store and barrier grid tube normally addresses the store in an orderly sequence of one line at a time, each new spot being adjacent to the preceding spot. This orderly sequence must be interrupted to service the raster reference system. There is one clock which drives the sequential deflection and another, in no way related, which drives the servo. Since the two clocks are not related, the deflection sequence may be interrupted at any of the 16,384 storage addresses and changed to one of the four servo addresses in a random manner. If the servo is disabled, the error signal out of the raster reference tube may be calibrated and used to measure deflection errors equivalent to those resulting from random addressing.

Full output of the servo results from a less than one-spot error, so small errors are easily measured.

The third method which was tried utilizes the output from the barrier grid tube. A deflection error is deliberately caused by adding a small current to the output of one side of the digital-to-analog converter and subtracting a like current from the complementary side. If the deflection is accurate before the error current is added, a reduction in readout voltage will result both when the error current is added positive to one side and negative to the complement and when the current is switched negative to the first side and positive to the complement. If there is a deflection error prior to adding the error current, switching the error current will cause a decrease in readout when it is switched in one sense and an increase in readout when it is switched in the other sense.

This method of measurement is the most accurate, because the error current is easily made as accurate as is the current for the digits in the digital-to-analog converter. This method revealed that an overshoot on the beam drive pulse caused the beam to miss the center of the stored charge, by as much as 0.1 spot on some barrier grid tubes, during the time the readout was being developed. An immediate improvement in the operation of the store resulted when the overshoot was reduced.

#### VIII. SUMMARY

The barrier grid tubes which are used guarantee a RAN (Read Around Number) of 150 for a 128 × 128 array of storage spots. To utilize the storage capabilities of the tube fully, a deflection system with an accuracy better than 0.1 per cent was developed. The speed of the deflection system had to be compatible with the 0.75-microsecond reading and 0.75-microsecond writing time capabilities of the tube. For the deflection to settle as accurately as this in a compatible time a 10 to 90 per cent rise time of 0.05 microsecond is required.

A comparison of high- and low-level digital-to-analog conversion systems resulted in the choice of the low-level system for present designs.

To insure a high RAN with a square array of 16,384 spots it is necessary to make the area covered by the array as large as possible without causing the corner spots to fall off the barrier grid. A raster reference servo system was developed to hold the array in a fixed position regardless of power supply or deflection amplifier drifts. The servo is a sampled error system.

Several methods of measurement were used, showing that the low-

level digital-to-analog system developed adequately meets the requirements of the barrier grid tubes now in use.

#### IX. ACKNOWLEDGMENTS

Most of the ground work leading to a successful deflection system was done by T. S. Greenwood and H. Raag. The guidance of R. E. Staehler and R. W. Ketchledge is particularly appreciated. The raster reference owes its success to the tube developed by M. Chruney, H. Ericsson, and J. A. McCarthy.

#### APPENDIX A

Deflection Amplifier Input Impedance [See Fig. 6(b)]

$$Z = rac{e_{

m in}}{i_{

m in}} = rac{e_{

m in}}{e_{

m in} - e_0},$$

$i = -rac{e_0}{R_5} - rac{e_0}{R_1},$

$e_0 = -rac{R_1 Z_5}{R_1 + Z_5}i,$

$i = G_m E_{gk} = G_m \left(e_{

m in} rac{R_3}{R_2 + R_3} - iR_4\right),$

$i = rac{G_m e_{

m in} R_3}{(1 + G_m R_4)(R_2 + R_5)},$

$e_0 = -\left(rac{R_1 Z_5}{R_1 + Z_5}\right) rac{G_m e_{

m in} R_3}{(1 + G_m R_4)(R_2 + R_3)},$

$Z = rac{e_{

m in} R_1}{e_{

m in} + \left(rac{R_1 Z_5}{R_1 + Z_5}\right) \left[rac{G_m e_{

m in} R_3}{(1 + G_m R_4)(R_2 + R_3)}\right],$

$Z = rac{R_1}{1 + \left(rac{R_1 Z_5}{R_1 + Z_5}\right) \left(rac{R_3}{R_2 + R_3}\right) \left(rac{G_m}{1 + G_m R_4}\right),$

$R_1 \approx 4 \times 10^3$

$Z_5 = 2500\Omega$  in parallel with 72  $\mu\mu$ f.

$rac{R_3}{R_2 + R_3} \approx 0.85 \ G_m \approx 0.06,$

$R_4 = 6\Omega,$

$Z \approx 73\Omega$  at dc.

#### APPENDIX B

Deflection Amplifier Output Impedance [See Fig. 7(a)]

$$Z = rac{e_{

m in}}{i_{

m in}} = rac{e_{

m in}}{i + rac{e_{

m in}}{Z_5}},$$

$i = G_m E_{gk} = G_m \left[ e_{

m in} \left( rac{Z_6}{R_1 + Z_6} \right) \left( rac{R_3}{R_2 + R_3} \right) - i R_4

ight],$

$Z = rac{1}{G_m \left( rac{Z_6}{R_1 + Z_6} \right) \left( rac{R_3}{R_2 + R_3} \right) + rac{1}{Z_5}},$

$$R_6 \approx 12 \times 10^3$$

$Z_0 \approx 34\Omega$  at dc.

#### REFERENCES

1. Greenwood, T. S., and Staehler, R. E., A High-Speed Barrier Grid Store, B.S. T.J., **37**, September 1958, p. 1195.

Hines, M. E., Chruney, M. and McCarthy, J. A., Digital Memory in Barrier Grid Storage Tubes, B.S.T.J., 34, November 1955, p. 1241.

Hoover, C. W., Jr., Staehler, R. E. and Ketchledge, R. W., Fundamental Concepts in the Design of the Flying Spot Store, B.S.T.J., 37, September 1958,

4. Joel, A. E., Jr., An Experimental Switching System Using New Electronic Techniques, B.S.T.J., 37, September 1958, p. 1091.