# Gold-Epitaxial Silicon High-Frequency Diodes

By D. KAHNG and L. A. D'ASARO

(Manuscript received July 19, 1963)

A diode based on the properties of an evaporated gold contact on n-type epitaxial silicon has speed comparable to point contact diodes. The space charge region at zero bias can be designed to penetrate up to the impurity tail at the interface, thus reducing series resistance. An encapsulated diode was made with a 1-mil diameter gold contact on an epitaxial layer 1.5 microns thick having a surface doping of  $1 \times 10^{15}$  donors per cm³. The zerobias RC product of this diode is less than  $1 \times 10^{-12}$  second. Under forward bias the electron transit time through the epitaxial layer is less than  $2 \times 10^{-11}$  second. The breakdown voltage of experimental diodes is greater than 10 volts. Stress aging experiments in an inert atmosphere show no deterioration of electrical properties at temperatures up to the gold-silicon eutectic (370°C). This diode was used as a harmonic generator at 11 gc with an efficiency comparable to that of a gallium arsenide point contact diode.

## I. INTRODUCTION

The metal-semiconductor rectifying contact in a variety of configurations called "point contact" has long been used for microwave rectification and amplification. This investigation shows that metal-semiconductor diodes can be designed and fabricated by large-area techniques with speeds adequate for application as fractional nanosecond switches or microwave mixers. In particular, a gold n-type silicon contact will be considered here. An estimate of the response time can be obtained from a calculation of the transit time of electrons through the space charge region and the RC time. The series resistance and capacitance of the diode are made small by using an epitaxial structure. Since the hole injection in these diodes at low currents is negligibly small, the response time can be independent of hole lifetime. In what follows, design of these diodes will be discussed, and the predictions of the preliminary design will be compared with experiment.

# II. DIODE STRUCTURE AND FABRICATION

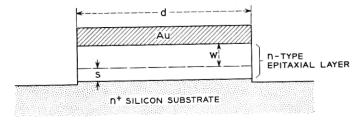

The structure of the diode is shown in Fig. 1. An epitaxial layer of n-type silicon is grown on an  $n^+$  substrate. A layer of gold is evaporated in a small dot over the epitaxial layer. The metal-semiconductor contact formed in this way has an internal potential which results in a space charge region in the silicon near the gold. The doping and thickness of the silicon is chosen so that at zero bias the space charge region of thickness w occupies most of the epitaxial layer. The remaining portion, s, is a region of high doping due to diffusion of impurities from the substrate.<sup>1,2</sup>

Experimental diodes were fabricated as follows. Silicon wafers of resistivity  $4 \times 10^{-3}$  ohm-cm with faces perpendicular to the  $\langle 111 \rangle$  direction were deposited with epitaxial layers of silicon by the hydrogen reduction of silicon tetrachloride. The film thickness in a typical diode is 1.5 microns. The surface doping of the n-type layers is  $2 \times 10^{14}$  to  $1 \times 10^{15}$  donors per cm<sup>3</sup>. The undeposited side of the wafers was provided with gold-antimony evaporated and alloyed ohmic contacts. These wafers were then subjected to cleaning consisting of oxidation and oxide removal steps. The wafers were cleaned immediately prior to gold evaporation. Gold evaporation was carried out in a vacuum of less than  $2 \times 10^{-6}$  mm Hg. Gold was evaporated through a molybdenum mask, confining the gold to a circular area 1 mil in diameter. After evaporation some of the diodes were etched, using the gold dots as masks. The etching removes the epitaxial region outside of the gold dots, thus preventing formation of large-area channels near the gold dots.

## III. RESPONSE TIME

The low-current response time is determined by the transit time of electrons through the space charge region and the RC charging time. The transit time is given approximately by  $\tau_t = w/v_s$ , where w is the space charge width and  $v_s$  is the average scattering limited velocity in the space charge region. The RC charging time can be estimated from the resist-

Fig. 1 — Structure of a gold-silicon epitaxial barrier diode.

ance of the unswept-out region of the epitaxial layer plus the spreading resistance in the substrate and the capacitance of the contact

$$RC = C_a \int_{\text{region}} \rho_e \, dx + \frac{C_a \rho_e d}{2} \tag{1}$$

where  $C_a$  is the capacitance per unit area of the diode,  $\rho_e$  is the resistivity of the epitaxial layer in region s,  $\rho_s$  is the resistivity of the substrate and d is the diameter of the contact.

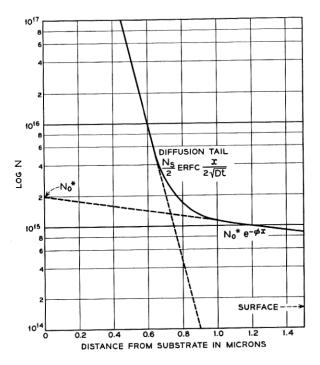

Calculation of the response time can be made for a case where the donor distribution in the epitaxial layer is known. In layers a few microns thick, the effect of diffusion from the substrate and the effect of the process of epitaxial growth on the distribution of impurities<sup>1</sup> need to be considered. The doping profile (concentration N versus distance x) may be approximately characterized by the form<sup>1,2</sup>

$$N = \frac{N_s}{2} \operatorname{erfc} \frac{x}{2\sqrt{Dt}} + N_0^* e^{-\phi x} + A(1 - e^{-\phi x})$$

(2)

where the first term is due to diffusion from the substrate of doping  $N_s$  with an effective diffusion coefficient D for a time t (an approximation), the second term is the substrate contribution to the film doping through the exchange of dopant between the solid and gas phase with parameters  $N_0^*$  and  $\phi$ , and the last term is the gas phase contribution to the film doping with an asymptotic value A for thick films. An example of an impurity distribution obtained in the fabrication of experimental gold-silicon epitaxial diodes is given in Fig. 2. The diffusion and exchange contributions to the doping are much larger than the gas phase contribution in the thicknesses used here. Within the lower doped region, one may approximate by a uniform doping for estimates of performance, since the film thickness is smaller than  $1/\phi$ .

The width of the space charge region at equilibrium in a uniformly doped material is given by

$$w = \left(\frac{2\epsilon V_D}{qN}\right)^{\frac{1}{2}} \tag{3}$$

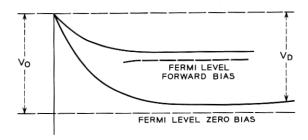

where  $\epsilon$  is the dielectric constant,  $V_D$  is the diffusion potential (shown in Fig. 3), q is the electron charge, and N is the donor concentration. In a typical case for these diodes the donor concentration in the region in which the exchange contribution dominates may be  $1 \times 10^{15}$ . The barrier potential for the gold-silicon contact ( $V_0$  in Fig. 3) is known from measurements of the forward and reverse characteristics and the

Fig. 2 — Impurity profile components for an epitaxial silicon film.

capacitance-voltage relation,<sup>4</sup> and is  $0.79 \pm 0.02$  ev for silicon dopings from 0.1 to 10 ohm-cm. At  $N_d = 1 \times 10^{15}$ , the Fermi level is 0.25 volt below the conduction band, leading to  $V_D = 0.54$  volt, and w = 0.67 micron. Since the edge of the space charge region falls in the diffusion tail, the series resistance of the diode is due to the doping in this tail. Integration over the doping distribution in Fig. 2 yields a zero-bias series resistance of 4.0 ohms.

Fig. 3 — Shape of the potential barrier under zero and forward bias.

The zero-bias capacitance can be found from

$$C = (\epsilon/w)A \tag{4}$$

where A is the diode area. For a 1-mil diameter diode, the expected zero-bias capacitance is about 0.05 pf. The capacitance of the encapsulation raises the total to about 0.3 pf, making the zero-bias RC product equal to  $1.2 \times 10^{-12}$  second for the diodes with a series resistance of 4 ohms.

The transit time of majority carriers through the space charge region at zero bias leads to an upper limit on the response time. For the case given above under zero bias, the transit time obtained from an assumed scattering limited velocity of  $5 \times 10^6$  cm/sec is  $2 \times 10^{-11}$  second. Under forward bias the width of the space charge region decreases, and hence the response time may be shorter than this estimate.

#### IV. HOLE INJECTION CONSIDERATIONS

The hole injection ratio is defined as

$$\gamma = j_p/(j_p + j_n) \tag{5}$$

where  $j_p$  is the hole current and  $j_n$  is the electron current crossing the junction. Diffusion theory<sup>5</sup> allows this expression to be written as

$$\gamma = q D_p p_n / L_p j_{ns} \tag{6}$$

where  $D_p$  is the diffusion constant for holes,  $p_n$  is the equilibrium concentration of holes in n-type material,  $L_p$  is the diffusion distance for holes, and  $j_{ns}$  is the saturation value of the electron current, which can be obtained in terms of "diode" theory <sup>6</sup> as

$$j_{ns} = A T^2 e^{-\beta V_0}. (7)$$

For  $N_d = 1 \times 10^{15}$  and the experimental values of A (=40) and  $V_0$  (=0.79 ev) from Ref. 4 one obtains  $\gamma \approx 1 \times 10^{-7}$ . Under low-current conditions the hole injection will not have a significant effect on the response time.

With increasing forward bias, the series resistance increases as the space charge region moves towards the gold-silicon junction. In the case of an extreme forward bias, the assumptions used earlier are not valid, and the hole current increases.<sup>7</sup> The series resistance may then be conductivity modulated and falls with continuously increasing current.

#### V. BREAKDOWN VOLTAGE

The avalanche breakdown voltage can be roughly estimated from the published ionization rate of electrons. One may obtain the breakdown

voltage in terms of empirically derived constants a and b as

$$V_B = bw/\ln aw \tag{8}$$

which gives  $V_B = 36$  volts with w = 0.9 micron. Experimental diodes show breakdown voltages which occasionally approach this value. Newer data based on microplasma free junctions would predict higher values.

# VI. ELECTRICAL MEASUREMENTS

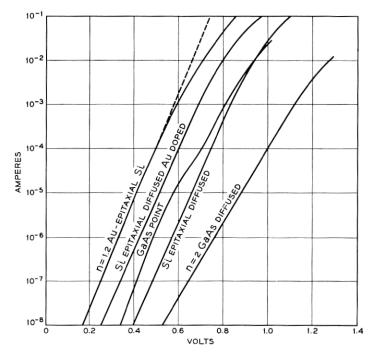

Experimental diodes in encapsulations typically show the following properties: breakdown voltage at 10  $\mu$ amps, 25 volts; series resistance at 100 ma, 3 ohms; zero-bias capacitance, 0.35 pf. These diodes have a forward V-I characteristic given in Fig. 4. The forward characteristic can be described by the empirical relation

$$I = I_s \exp \frac{q}{nkT} (V-IR) \tag{9}$$

in which n is an empirical quantity and R is a series resistance. The "diode" theory predicts the forward characteristics of the form of (9) with n=1. The departure of n from unity may be attributable to currents generated at traps within the space charge region. Experiments on diodes of larger diameter suggest that these traps are located around the periphery of the diode, at the gold-silicon interface. In general, n is a continuously varying quantity with the current. The series resistance may decrease in the high current density region due to increased minority carrier injection. Characteristics of other diodes normalized to 1-mil diameter mesas are given for comparison in Fig. 4.

# VII. RESPONSE TIME MEASUREMENTS

The response time of the experimental diodes was examined by a pulse recovery measurement. No storage time as large as the resolving time of the equipment, which is 1 nanosecond, was found.

A further measurement of an experimental diode was made by A. F. Dietrich using a method previously described for generating carrier pulses at a frequency of 11 gc.<sup>10</sup> In this method the RF pulses are generated directly from the harmonics of the envelope frequency that is found at the beginning or the end of the pulse transient of the diode. The power output at 11 gc was comparable to that previously obtained with a silicon snap-back diode (FD-100) or a GaAs point contact diode. These

Fig. 4 — Forward bias voltage-current characteristics of a gold-epitaxial silicon diode, in comparison with other diodes. Diode diameters are 1 mil, except for the GaAs point contact. The dotted line has a slope of n=1.2.

results indicate that the response time of the diode under forward bias of 60 ma is roughly 0.1 nanosecond.

## VIII. STRESS AGING EXPERIMENT

A group of eight diodes was subjected to stress aging in an effort to establish the expected reliability of the gold-silicon contact. These diodes were all mounted on the same header in order to provide an equal stress condition. Heating them in an inert atmosphere for one-hour periods at increasing temperatures up to the gold-silicon eutectic temperature (370°C) produced no significant degradation in their forward or reverse characteristics. Another group of eight diodes was heated at 360°C for 64 hours. These diodes also showed no significant degradation in their V-I characteristics. In another experiment, diodes heated in air showed rapid degradation above 200°C. These experiments indicate that the gold-silicon contact can probably be made adequately stable for device use.

### IX. CONCLUSIONS

The design described above has been found to yield experimental devices which are sufficiently fast and stable to be useful as computer diodes or as microwave mixer diodes. Another design in which the space charge region penetrates part way through the epitaxial layer may also be of interest as a varactor. One may expect that the large-area techniques used in the design and fabrication of these diodes will lead to more reproducible and stable devices than point contact diodes with similar frequency response.

#### REFERENCES

- Thomas, C. O., Kahng, D., and Manz, R. C., Impurity Distribution in Epitaxial Silicon Films, J. Electrochem. Soc., 109, No. 11, November, 1962, p.

- Kahng, D., Thomas, C. O., and Manz, R. C., Anomalous Impurity Diffusion in Epitaxial Silicon Near the Substrate, J. Electrochem. Soc., 109, No. 11,

- November, 1962, p. 1106.

3. Theurer, H. C., Epitaxial Silicon Films by Hydrogen Reduction of SiCl<sub>4</sub>, J. Electrochem. Soc., 108, No. 7, July, 1961, p. 649.

- 4. Kahng, D., Conduction Properties of the Au-n-type Si Schottky Barrier, Solid-State Electronics, 6, 1963, p. 281.

- 5. Henisch, H. K., Rectifying Semiconductor Contacts, Oxford University Press,

- 1957, p. 229.

6. Bethe, H. A., Theory of the Boundary Layer of Crystal Rectifiers, MIT Radiation Lab Report 43/12, November 23, 1942.

- 7. Scharfetter, D. L., Anomalously High Minority Carrier Injection in Schottky Diodes, IRE-AIEE Solid State Device Research Conference, Michigan State University, June, 1963.

- Maserjian, J., Determination of Avalanche Breakdown in p-n Junctions, J. Appl. Phys., 30, No. 10, October, 1959, p. 1613.

Lee, C. A., Logan, R. A., Batdorf, R. L., Kleimack, J. J., and Wiegmann, W., to be published.

- to be published.

- Dietrich, A. F., 8- and 11-GC Nanosecond Carrier Pulses Produced by Harmonic Generation, Proc. I.R.E., 49, May, 1961, p. 972.