# A Depletion-Load, p-Channel, Bipolar-IGFET Technology

By G. MARR and G. L. MOWERY

(Manuscript received April 25, 1974)

A high-performance, depletion-load, bipolar-IGFET technology is described. The optimization of device and circuit parameters, the ion-implanted depletion-load fabrication process, and the high-speed input and output circuits, which allow direct interface with the TTL circuit family, are discussed.

#### I. INTRODUCTION

Since the development of the low-threshold  $(V_T=-1 \text{ volt})$  metalgate p-channel  $\text{Al}_2\text{O}_3\text{-SiO}_2$  igfet technology,¹ further technological advances have been made to improve circuit speed and interface flexibility of igfet circuits. Two significant improvements have been the incorporation of bipolar-igfet (Bigfet)² devices on the same monolithic silicon-integrated circuit (SiC) and the application of ion implantation to fabricate depletion-load igfet's.³ These have resulted in an igfet technology whose circuits are completely compatible with the standard 5-volt bipolar the family in terms of input and output levels as well as power supply. Furthermore, the relatively high functional packing density of the igfet technology makes it an extremely attractive option in MSI/LSI applications. These have been successfully realized in the design and fabrication of several Bell System catalog and custom circuits.

In this paper, the technology characteristics of the depletion-load BIGFET technology are described.

#### II. DEPLETION-LOAD INVERTER

### 2.1 Circuit characteristics

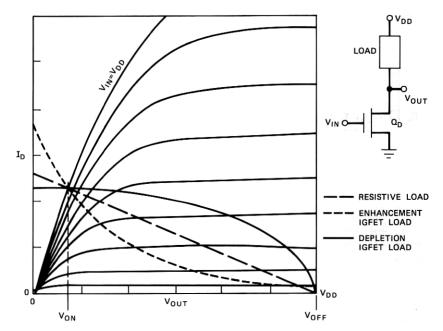

The advantages of the depletion-load inverter over a similar allenhancement or resistor-load inverter become obvious when we consider the various load-line characteristics. In Fig. 1, the load lines of a resistive load, an enhancement-igfet load, and a depletion-igfet load are shown over the family of IV curves for the enhancement-

Fig. 1—Inverter load-line characteristics.

IGFET driver  $(Q_D)$ . The three load lines are chosen to intercept at the same point in the  $V_{\rm in}=V_{DD}$  and  $V_{\rm in}=0$  characteristics curves to reflect the fact that they will produce the same output dc levels. The area under the load line represents the transient power dissipated during one logic transition. For a given capacitive loading on the inverter output node, the transient power dissipation is proportional to the frequency of operation. Therefore, the area under the load line is directly proportional to the maximum operating frequency of the inverter. The speed advantage of the depletion load is apparent because it has the largest area between  $V_{\rm out}=V_{\rm on}$  and  $V_{\rm out}=V_{\rm off}$ .

# 2.2 Circuit equations

In this section, the approximate circuit equations of the depletionload inverter are reviewed. In spite of their inexactness, they are useful because they provide insight into the functional dependence of circuit parameters on device parameters. However, the final choice of device parameters, discussed in Section 2.3, was based on more exact computer calculations.

Assuming the gradual-channel approximation, the output levels  $(V_{\text{on}} \text{ and } V_{\text{off}})$  and the corresponding single-stage noise margins  $(V_{M1} \text{ and } V_{M2})$  of a depletion-load inverter with  $Q_D$  on and off, respectively,

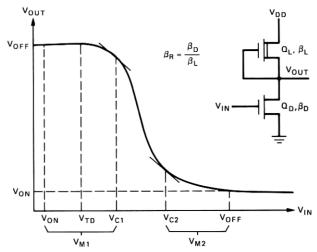

Fig. 2—Depletion load inverter.

as shown in Fig. 2, may be given by4

$$V_{\rm on} \cong \frac{V_a^2}{2(V_{DD} - V_{TD})} \tag{1}$$

$$V_{\rm off} = V_{\rm DD} \tag{2}$$

$$V_{M1} = |V_{C1} - V_{on}| \tag{3}$$

$$V_{M2} = |V_{C2} - V_{\text{off}}|, (4)$$

where

$$V_{C1} = \frac{V_a}{(1+\beta_R)^{\frac{1}{2}}} + V_{TD} \tag{5}$$

$$V_{C2} = \sqrt{\frac{4}{3} \cdot V_a} + V_{TD} \tag{6}$$

$$V_a = \sqrt{\frac{V_{TL}^2}{\beta_R}}, (7)$$

and where

$V_{TD}$ ,  $V_{TL}$  = threshold voltages of  $Q_D$  and  $Q_L$ , respectively,

$V_{DD}$  = supply voltage,

$\beta_D$ ,  $\beta_L$ ,  $\beta_R = \text{IGFET gain parameter of driver and load and their ratio.}$

The propagation delay  $(t_d)$  is directly related to the inverter-output rise time  $(t_r)$  and fall time  $(t_f)$ . Since the rise-time charging current is given by  $I_r = (\beta_L/2) \cdot (V_{TL})^2$ ,  $t_r$  may be approximated as

$$t_r = \frac{2V_{DD}C}{\beta_L V_{TL}^2},\tag{8}$$

where C is the output capacitance and, neglecting interconnection capacitance, may be expressed in terms of  $\beta_D$  as

$$C = \frac{l_D^2 \beta_D}{\mu} (1 + F), \tag{9}$$

where  $l_D$  is the channel length of  $Q_D$ ,  $\mu$  is the mobility of carriers in the channel, and F is the number of similar inverter gates to be driven (fan-out). If interconnection capacitance is expressed as equivalent fan-out, eq. (9) is still applicable. Substituting (9) into (8) results in

$$t_r = \frac{2V_{DD}\beta_R l_D^2}{\mu \cdot V_{TL}^2} (1 + F). \tag{10}$$

Likewise, since the fall-time discharging current,

$$I_f = (\beta_D/2)(V_{DD} - V_{TD})^2 - (\beta_L/2)V_{TL}^2$$

the fall time of the output voltage may be approximated as

$$t_f = \frac{2V_{DD}l_D^2(1+F)}{\mu[(V_{DD} - V_{TD})^2 - V_{TL}^2/\beta_R]}.$$

(11)

Since  $t_d$  is proportional to  $(t_r + t_f)$ , we observe from (10) and (11) that  $t_d$  is directly proportional to  $l_D^2$ , F, and  $V_{DD}$ . A more important observation, perhaps, is that as  $V_{TL}^2/\beta_R$  increases,  $t_r$  decreases and  $t_f$  increases. Thus, depletion-load inverters designed for optimal speed have  $t_r$  and  $t_f$  nearly equal.

A final useful relationship is the power-delay product of the inverter. Using the average power for  $P_D$  for small  $V_{TL}^2/\beta_R$ ,

$$P_D t_d \sim P_D t_r \sim (V_{DD} I_L) \left( \frac{V_{DD} C}{I_L} \right) \sim V_{DD}^2 C \sim \frac{V_{DD}^2 l_D^2 \beta_D (1+F)}{\mu}$$

,

where  $C_D$  is the gate capacitance of  $Q_D$ , and  $P_D t_d$  is completely independent of  $V_{TL}$ . However, for larger values of  $V_{TL}^2/\beta_R$ ,

$$P_D t_d \sim P_D t_f \sim \frac{V_{DD}^2 \beta_D l_D^2 (1+F)}{\mu \left[ \frac{\beta_R (V_{DD} - V_{TD})^2}{V_{TL}^2} - 1 \right]},$$

and  $P_D t_d$  increases quadratically as  $|V_{TL}|$  increases until  $|V_{TL}| \sim \sqrt{\beta_R} |V_{DD} - V_{TD}|$ .

As we stated earlier, the preceding approximate equations provide insight into the dependence of circuit parameters on device parameters for a depletion-load IGFET inverter. This is appropriate for characterizing the properties of any depletion-load IGFET random logic circuit, normally comprising an assortment of n-input NAND and NOR gates,

because both these logic gates can be analytically reduced to an equivalent depletion-load IGFET inverter.

# 2.3 Selection of $V_{TL}$ and $\beta_R$

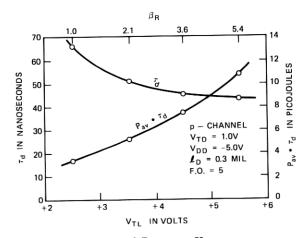

In this section, the method of determining the parameters of the depletion-load IGFET and the corresponding  $\beta_R$  are discussed. Since the equations developed in Section 2.2 are only approximate, more exact calculations were made using the circuit analysis program SERVICE. In this way, the voltage dependence of  $V_{TL}$  was properly accounted for.

The objectives and constraints of the technology were chosen to be:

- (i) Single-supply voltage  $V_{DD} = -5 \pm 0.5$  volt.

- (ii)  $V_{TD} = -1 \pm 0.4$  volt at end of life.

- $(iii) |V_{on}| \leq |V_{TD}|.$

- (iv)  $V_{M1}$  and  $V_{M2} \ge 0.5$  volt.

The problem is then, simply: Given these conditions, determine  $\beta_R$  and  $V_{TL}$  such that  $t_d$  is nearly a minimum for an assumed typical fanout of five from each inverter. The net result is a family of  $t_d$  vs.  $V_{TL}$  curves. Since  $V_{\text{on}}$ ,  $V_{M1}$ , and  $V_{M2}$  are functions of  $V_{TL}$ , a different  $\beta_R$ , the minimum value consistent with conditions (iii) and (iv) was chosen for every value of  $V_{TL}$  used. A nominal  $t_d$  vs  $V_{TL}$  curve is shown in Fig. 3, where the  $P_D t_d$  product is also plotted against the same  $V_{TL}$  scale. As can be seen from the curve, the value of  $t_d$  reaches a nearly minimum constant value for  $V_{TL} \sim 4.5$  volts, when  $t_r \sim t_f$ . We may further note that the  $P_D t_d$  product increases approximately quadratically as  $V_{TL}$  increases. Based on this type of plot of all com-

Fig. 3— $\tau_d$  and  $P_{av} \cdot \tau_d$  vs.  $V_{TL}$  curve.

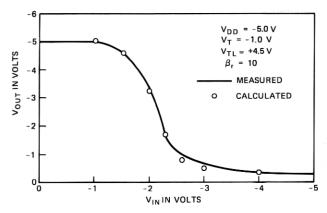

Fig. 4—Depletion-load inverter transfer curve.

binations for different limits of  $V_{DD}$  and  $V_{TD}$ , an optimal  $V_{TL} = 4.5$  $\pm$  0.5 volt was chosen, corresponding to a minimum design  $\beta_R$  of 5.

Figure 4 shows a calculated and a measured dc transfer curve. The good agreement between the two is an indication of the validity of the present work.

## III. DEPLETION-LOAD FABRICATION AND CHARACTERISTICS

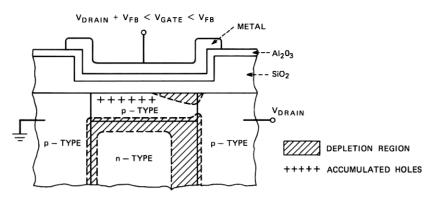

A proven method of fabricating depletion igfer's is the use of a selective ion implant through the gate dielectric in the IGFET channel regions. To achieve good control of the device properties, it is desirable to have the majority of the implanted ions in the silicon rather than in the gate dielectric, which requires 120 keV for the boron ions used. The resulting device no longer behaves exactly like the normal IGFET

Fig. 5—Depletion igfet cross-sectional view.

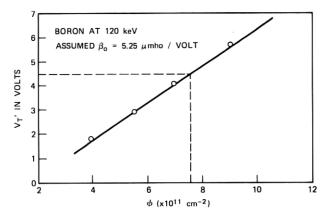

Fig. 6—Effective threshold vs. implant dose.

in which conduction takes place only in the surface inversion. It is actually a deep depletion igfet with a subsurface channel, whose conductivity is modulated both by surface depletion and by the channel to substrate junction as shown in Fig. 5. The current-voltage characteristics of such a deep depletion igfet have been previously described.<sup>3</sup>

To achieve a reproducible profile of the ion-implanted dopants in the silicon, it is desirable to minimize the duration and extent of high temperature anneal treatment after the ion implantation. Since all the diffusion processes take place before the gate oxidation, the latter is the last high temperature step. Therefore, ion implantation is performed after the gate oxidation process. The photomask step for the boron implantation utilizes a thick photoresist layer (1.4 μm) that is opaque to the 120-keV boron ions. Furthermore, since the required implantation dose of 7.6 × 10<sup>11</sup> cm<sup>-2</sup> is rather low, no damage to the gate dielectric is either expected or observed in the fabricated samples. The needed anneal<sup>6</sup> of implanted species is achieved in a subsequent process step when the masking SiO<sub>2</sub>\* is deposited over the whole wafer at 900°C for 20 minutes.

Figure 6 shows the effective threshold  $V_T' = \sqrt{(2I/\beta)}$  as a function of the implantation dose of boron at 120 keV. The current is measured when gate and source are common and the drain biased at -5 volts. We observe that the  $V_T' - Q$  curve is essentially linear over a fairly wide range of dose  $(2 \times 10^{11} \text{ to } 9 \times 10^{11} \text{ cm}^{-2})$ .

<sup>\*</sup>The metal-gate IGFET (Ref. 1) has a double layer Al<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub> for its gate dielectric. The deposited oxide is needed to serve as a mask when Al<sub>2</sub>O<sub>3</sub> is selectively etched.

### IV. INTERFACE CIRCUITS

To allow realization of the speed advantages offered by the depletionload and bigfet technologies, two buffer circuit configurations have been developed to facilitate efficient interface between inputs and outputs of bigfet sic's as well as to inputs and outputs of ttl(l) circuits. These two circuits are the level-shifting input circuit and the low-impedance output driver.

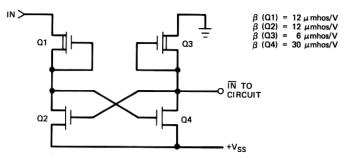

# 4.1 Input interface

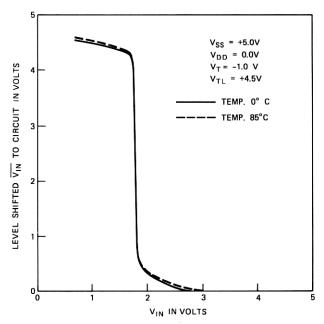

It is necessary that the input voltage to an igfet inverter be within one device threshold of substrate potential to assure complete turn-off of that inverter. Since this requirement is not met for the 1-volt threshold p-channel technology by either ttl or bigfet output levels, the input level shifting circuit has been designed to accept these logical 1 levels. The schematic of the input circuit is shown in Fig. 7. The corresponding dc transfer curves are shown in Fig. 8. The internal feedback configuration of the level shifter produces a very sharp gain characteristic that lowers the required level for logic 1 and also provides increased noise margin and input signal wave shaping. In the design of this circuit, both the  $\beta$  ratio of Q1 to Q2 and the  $\beta$  ratio of Q3 to Q4 strongly affect the acceptable input voltage range. The  $\beta$  ratio of Q1 to Q3 is not critical, but may be chosen to produce minimum propagation delay of signals through the input level shifter in a specific application.

A further constraint on the  $\beta$  values of Q1 and Q2 is the fan-out desired from  $\mathtt{TTL}(\mathtt{L})$  outputs and from bigget outputs into this level shifting input. During a 1 to 0 transition of the input voltage, igget's Q1 and Q2 conduct current from the substrate to the input node. The requirement of conducting this current to ground while maintaining a valid 0 level at the input determines the fan-out from a given output to the level shifting input circuits. Maximum 0 level  $V_{\rm in}$  to the level

Fig. 7—Inverting level shifting input circuit.

Fig. 8-Inverting level shifter transfer curves.

shifting input inverter is  $V_{SS} = 3.4$  volts, which is 1.1 volts for  $V_{SS} = 4.5$  volts. Allowing 0.4-volt interface noise margin requires that the input voltage be  $\leq 0.7$  volt for the 0 level. The TTL(L) output is rated at 28 mA to ground at 0.7 volt. The level shifting input inverter of Fig. 7 can conduct  $\beta \times 4.2$   $\mu$ A during a 1 to 0 transition, where  $\beta = \beta_{Q1}$  or  $\beta_{Q2}$  is expressed in micromhos per volt. Therefore, the fan-out from TTL(L) to level shifting inputs is fan-out =  $6667/\beta$ , where  $\beta = \beta_{Q1}$  or  $\beta_{Q2}$ . Similarly, the bigfet output with maximum output resistance of 2.1 kilohms can conduct 0.333 mA at 0.7 volt. Therefore, fan-out from bigfet outputs to level shifting inputs is fan-out =  $79/\beta$ , where  $\beta = \beta_{Q1}$  or  $\beta_{Q2}$ .

The circuit of Fig. 7 has been used in various depletion-load circuits for both custom and general-purpose applications. It provides

|                       | Min.         | Max.                         |

|-----------------------|--------------|------------------------------|

| $V_{in} 0$            | 0.0          | $V_{SS} - 3.4 \text{ volts}$ |

| $V_{\mathtt{in}} \ 1$ | $V_{SS}=2.2$ | ${V}_{ss}$ volts.            |

## 4.2 Output interface

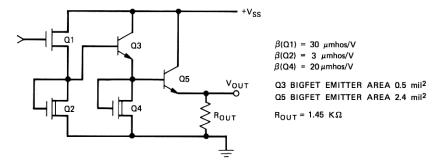

The BIGFET output circuit configuration is shown in Fig. 9. This circuit provides an ideal coupling between the high-impedance igfet's and the desired low-output impedance. The current gain provided by

Fig. 9—BIGFET SIC output circuit.

the Darlington bigfet structure permits the gate capacitance of Q1 to be as small as that normally used internally in an igfet circut. Since average power dissipation of the output circuit is  $\alpha(R_{\text{out}})^{-1}$ , it is desirable to make  $R_{\text{out}}$  large. But the maximum allowed value of  $R_{\text{out}}$  is determined by the input characteristics of TTL(L),  $-240~\mu a$  at 0.4-volt input logical 0. Consequently,  $R_{\text{out}}$  is nominally 1.45 kilohms, and the other device values are as shown in Fig. 9 for this bigfet output configuration with fan-out = 1 capability to TTL(L) circuits.

The value of  $R_{\rm out}$ , the  $V_{\rm be}$  voltage drops of Q3 and Q5 operating as a Darlington pair, and the bigfet emitter area of Q5 are designed to prevent Q5 from entering the saturation region, which would significantly increase the turn-off time of Q5.

The circuit of Fig. 9 has been used in various depletion-load circuits for both custom and general-purpose applications. It provides

|                        | Min.         | Max.                |

|------------------------|--------------|---------------------|

| $V_{ m out}0$          | 0.0          | 0.4 volt            |

| $V_{\mathtt{out}} \ 1$ | $V_{SS}-1.7$ | $V_{SS}-1.2$ volts. |

## V. SUMMARY

The p-channel depletion-load BIGFET process has been demonstrated to be a successful technology for producing BIGFET SIC'S. Circuit behavior has been approximately described using simplified circuit equations, and exact circuit behavior has been characterized using results from computer circuit analysis programs. Good agreement has been achieved between experimental results and circuit simulation. The application of ion implantation to the fabrication of depletion mode IGFET load devices has been described, and a correlation is shown between the effective threshold voltage and implant dose. Finally, the input and output buffer circuits, which allow interface between BIGFET SIC'S and TTL(L) circuits, are presented.

#### REFERENCES

H. E. Nigh, J. Stach, and R. M. Jacobs, "A Sealed Gate IGFET," Solid State Dev. Res. Conf., Santa Barbara, California, June 19-21, 1967.

G. Marr, G. T. Cheney, E. F. King, and E. G. Parks, "A Fast Bipolar-IGFET Buffer-Driver," B.S.T.J., 51, No. 2 (February 1972), p. 363.

J. R. Edwards and G. Marr, "Ion Implanted Depletion-Mode IGFET," IEEE Trans. Electron Dev., 20, No. 3 (March 1973), p. 283.

T. Masuhara, M. Nagata, and N. Hashimoto, "A High Performance n-channel MOS LSI Using Depletion-Type Load Elements," IEEE J. of Solid State Circuits, SC-7, No. 3, 1972, p. 224.

J. D. Leggett and E. B. Kozemchak, "The Domain Simulation of Non-Linear Networks by Nodal Analysis," Conf. Record of 5th Asilomar Conference on Circuits and Systems, November 1971, pp. 531-534.

T. E. Seidel and A. U. MacRae, Trans. AIME, 245, 1969, p. 491.