## HEWLETT-PACKARD JOURNAL

© Copr. 1949-1998 Hewlett-Packard Co.

# JOURNAL

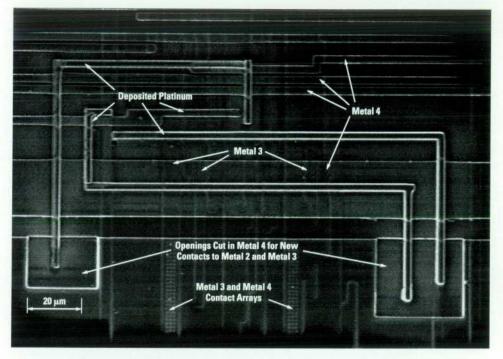

#### Articles

| 2 | <b>PPA Printer Software Driver Design</b> , by David M. Hall, Lee W. Jackson, Katrina Heiles, Karen E. Van der Veer, and Thomas J. Halpenny |

|---|---------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | PPA Printer Firmware Design, by Erik Kilk                                                                                                   |

| 1 | <b>PPA Printer Controller ASIC Development</b> , by John L. McWilliams, Leann M. MacMillan, Bimal Pathak, and Harlan A. Talley              |

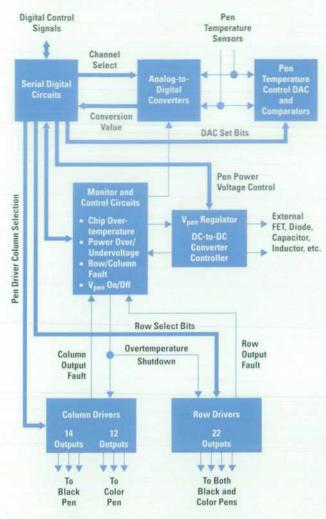

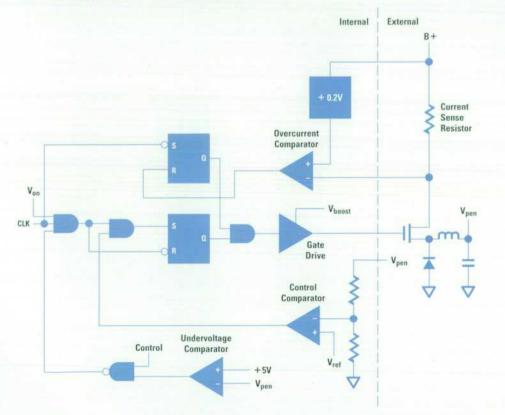

| 3 | Next-Generation Inkjet Printhead Drive Electronics, by Huston W. Rice                                                                       |

| 3 | The PA 7300LC Microprocessor: A Highly Integrated System on a Chip, by Terry W. Blanchard and Paul G. Tobin                                 |

| 5 | Configurability of the PA 7300LC                                                                                                            |

| 3 | Functional Design of the PA 7300LC, by Leith Johnson and Stephen R. Undy                                                                    |

| 2 | Timing Flexibility                                                                                                                          |

Executive Editor, Steve Beitler • Managing Editor, Charles L. Leath • Senior Editor, Richard P. Dolan • Assistant Editor, Robin Everest Publication Production Manager, Susan E. Wright • Distribution Program Coordinator, Renée D. Wright • Layout/Illustration, John Nicoara Webmaster, John Hughes

#### Advisory Board

Rajeev Badyal, Integrated Circuit Business Division, Fort Callins, Colorado William W. Brown, Integrated Circuit Business Division, Santa Clara, California Rajesh Desai, Commercial Systems Division, Cupertino, California Bernhard Fischer, Böblingen Medical Division, Böblingen, Germany Douglas Gennetten, Greeley Hardcopy Division, Greeley, Colorado Gary Gordon, HP Laboratories, Palo Alto, California Mark Gorzynski, Inkjet Supplies Business Unit, Corvallis, Oregon Matt J. Harline, Systems Technology Division, Roseville, California Kiyoyasu Hiwada, Hachigi Semiconductor Test Division, Tokyo, Japan Bryan Hoog, Lake Stevens Instrument Division, Forerett, Washington C. Steven Joiner, Optical Communication Division, Santa Rosa, California Roger L. Jungerman, Microwave Technology Division, Santa Rosa, California Ruby B. Lee, Networked Systems Group, Cupertino, California Swee Kwang Lim, Asia Peripherals Division, Waldbronn, Germany Alfred Maute, Waldbronn Analytical Division, Waldbronn, Germany

Andrew McLean, Enterprise Messaging Operation, Pinewood, England Dona L. Miller, Worldwide Customer Support Division, Mountain View, California Mitchell J. Mlinar, HP-EEsof Division, Westlake Village, California Michael P. Moore, VXI Systems Division, Loveland, Colorado M. Shahid Mujtaba, HP Laboratories, Palo Alto, California Steven J. Narciso, VXI Systems Division, Loveland, Colorado Danny J. Oldfield, Electronic Measurements Division, Colorado Springs, Colorado Garry Orsolini, Software Technology Division, Roseville, California Ken Poulton, HP Laboratories, Palo Alto, California Ginter Riebesell, Böblingen Instruments Division, Böblingen, Germany Michael B. Saunders, Integrated Circuit Business Division, Corvallis, Dregon Philip Stenton, HP Laboratories Bristol, Bristol, England Stephen R. Undy, Systems Technology Division, Fort Collins, Colorado Jim Willits, Network and System Management Division, Fort Collins, Colorado Koichi Yanagawa, Kobe Instrument Division, Kobe, Japan

#### ©Hewlett-Packard Company 1997 Printed in U.S.A.

| 69 | Verifying the Correctness of the PA 7300LC Processor, by Duncan Weir and Paul G. Tobin                                                                           |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71 | Random Code Generation                                                                                                                                           |

| 73 | An Entry-Level Server with Multiple Performance Points, by Lin A. Nease, Kirk M. Bresniker,<br>Charles J. Zacky, Michael J. Greenside, and Alisa Sandoval        |

| 82 | A Low-Cost Workstation with Enhanced Performance and I/O Capabilities, by Scott P. Allan, Bruce<br>P. Bergmann, Ronald P. Dean, Diane Jiang, and Dennis L. Floyd |

| 89 | Testing Safety-Critical Software, by Evangelos Nikolaropoulos                                                                                                    |

| 92 | Another Approach to Testing: Inspections                                                                                                                         |

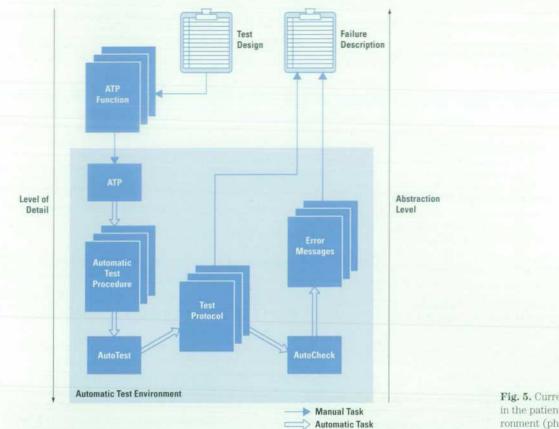

| 95 | A High-Level Programming Language for Testing Complex Safety-Critical Systems, by Andreas Pirrung                                                                |

| 97 | Structural Testing, Random Testing, and Statistical Structural Testing                                                                                           |

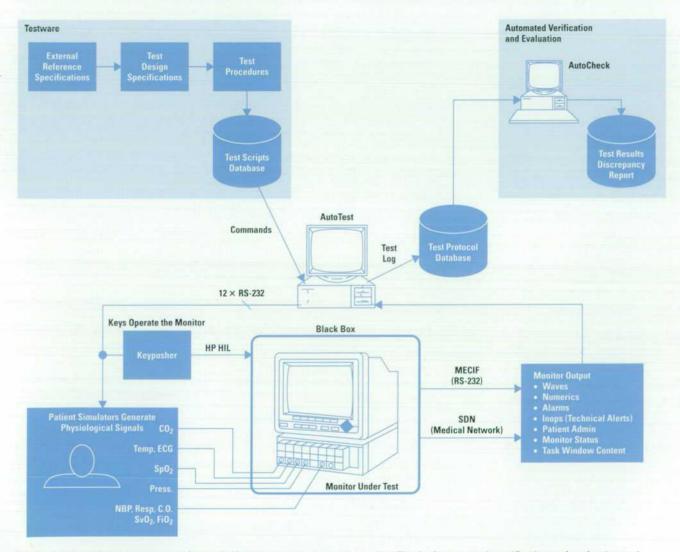

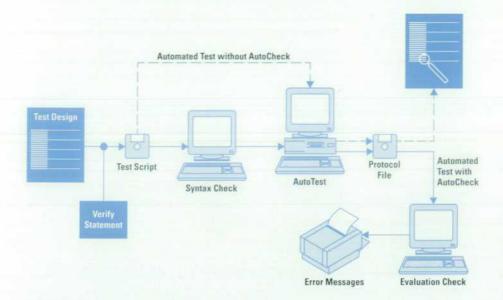

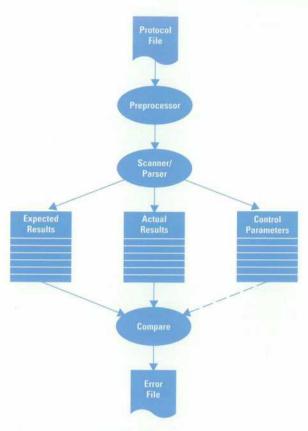

| 03 | An Automated Test Evaluation Tool, by Jörg Schwering                                                                                                             |

| 09 | Effective Testing of Localized Software, by Evangelos Nikolaropoulos, Jörg Schwering, and Andreas Pirrung                                                        |

|    | Departments                                                                                                                                                      |

- 4 In this Issue

- 5 Cover

- 5 What's Ahead

- 112 Authors

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. To receive an HP employee subscription you can send an e-mail message indicating your HP entity and mailstop to Idc\_litpro@hp-paloalto-gen13.om.hp.com. Qualified non-HP individuals, libraries, and educational institutions in the U.S. can request a subscription by either writing to: Distribution Manager, HP Journal, M/S 20BH, 3000 Hanover Street, Palo Alto, CA 94304, or sending an e-mail message to: hp\_journal@hp.com. When submitting an address change, please send a copy of your old label to the address on the back cover. International subscriptions can be requested by writing to the HP headquarters office in your country or to Distribution Manager, address above. Free subscriptions may not be available in all countries.

The Hewlett-Packard Journal is available online via the World Wide Web (WWW). The uniform resource locator (URL) is:

#### http://www.hp.com/hpj/journal.html

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HPrelated research or solutions to technical problems made possible by using HP equipment are also considered for publication. Before doing any work on an article, please contact the editor by sending an e-mail message to hp\_journal@hp.com.

Copyright © 1997 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice appears stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Managing Editor, Hewlett-Packard Journal, M/S 20BH, 3000 Hanover Street, Palo Alto, CA 94304 U.S.A.

#### In this Issue

One of the most competitive areas in the personal computer market today is the race to provide printing solutions to meet the needs of the entire family. The specifications for a successful printer in this arena include technologies that provide continuous improvement in throughput and print quality, low cost, attractive small size, quiet operation, ease of use, and designs that lend themselves to high-volume production.

Design teams at Hewlett-Packard divisions that are responsible for HP color inkjet printers decided to take a phased approach to meet the challenges posed by these specifications. The HP DeskJet 820C (page 6) is the first product resulting

from this evolutionary product plan. The DeskJet 820C contains a writing system, print mechanism, and package leveraged from the HP DeskJet 850C and a new electronic, firmware, and software architecture called the Printing Performance Architecture (PPA).

PPA grew out of the recognition that newer generations of personal computers have the bandwidth to take on some of the computing tasks typically relegated to the printer, and many software applications are rapidly moving away from MS-DOS<sup>®</sup> to a Microsoft Windows<sup>®</sup> environment. With this realization, the design teams developed a software, firmware, and digital electronics architecture that uses the computing resources of the PC instead of duplicating these resources in the printer. This architecture helped to lower the cost of the printer by reducing RAM from 1M bytes to 128K bytes, ROM from 2M bytes to 64K bytes, and the gate count of the largest ASIC by 25%.

With the reduction in the logic-supporting hardware in the DeskJet 820C, printer functions such as swath cutting and data formatting were moved into the software driver. The article on page 12 discusses the design of the PPA printer software driver, which implements functions traditionally found in the printer, handles PPA communication between the host and the printer, and provides PCL emulation for DOS application support.

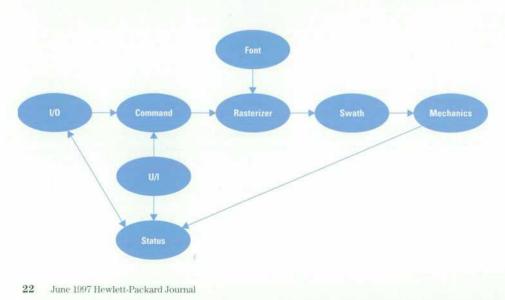

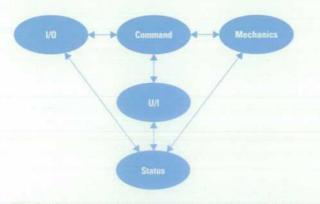

Because so many printer functions are implemented in the host software driver, fewer functions are needed in the firmware for the DeskJet 820C. As described in the article on page 22, "Don't touch the dots" was the firmware designers' golden rule. This means that firmware in the printer was designed so that it is only responsible for taking the formatted data from the host and sending commands to the motor and print cartridge to place the dots at the appropriate places on the paper. The printer firmware is also responsible for user interface and status functions.

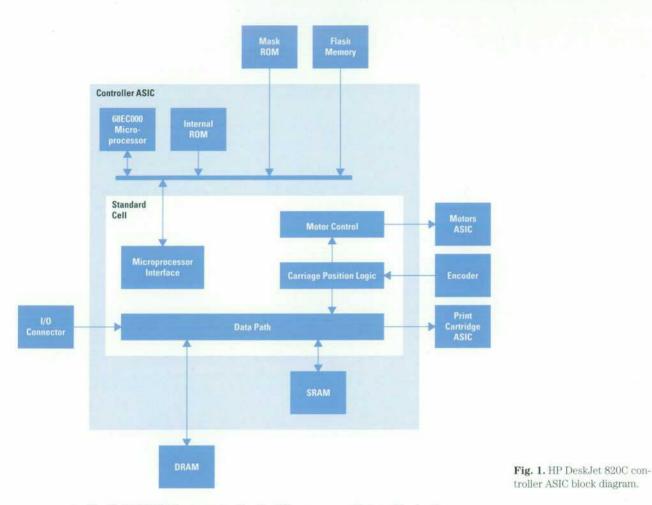

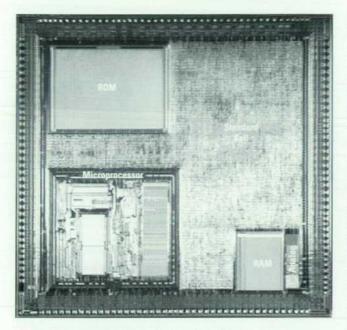

ASIC development for the PPA printer controller and the inkjet printhead drive electronics is described in the articles on pages 31 and 38 respectively. A typical digital controller for a printer contains a microprocessor to control the printer, RAM for incoming data, ROM for firmware, and custom logic for printerspecific functions. For the DeskJet 820C, these functions were integrated on one chip and optimized to meet the requirements of PPA. The pen drive electronics are responsible for driving signals to eject the ink from the pen and providing a control system to maintain a constant temperature in the active area of the pen. For the DeskJet 820C's pen drive electronics, the functions of four ICs were integrated in one chip, and all the electronics related to the pens were moved onto the carriage's printed circuit assembly.

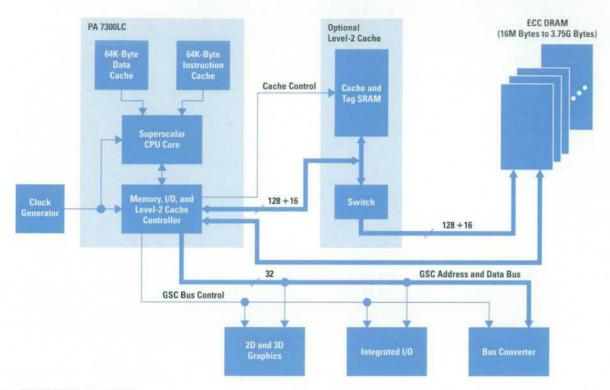

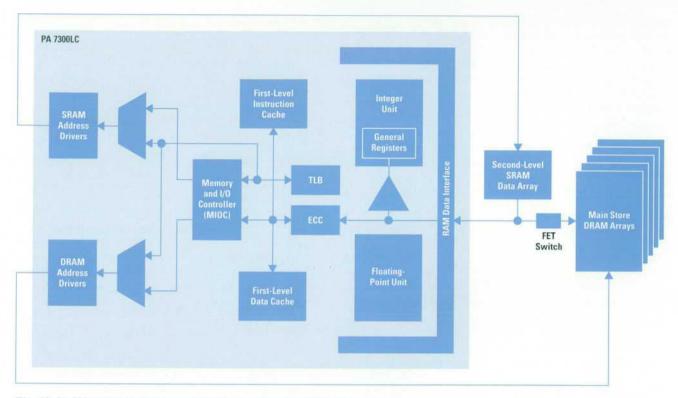

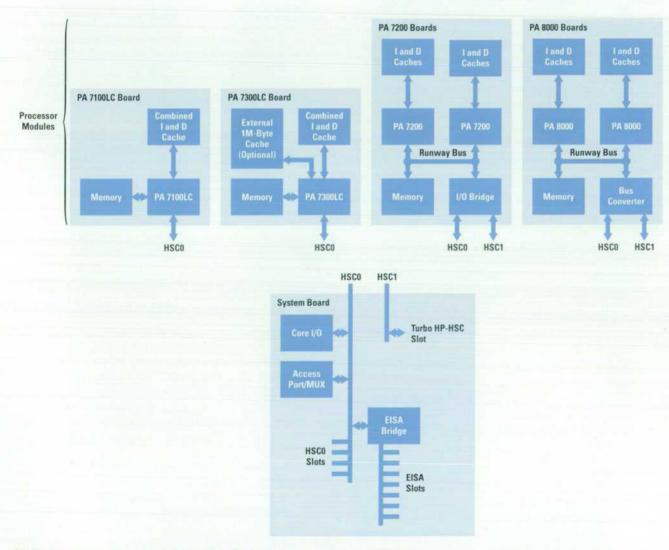

Today, key design decisions associated with developing a microprocessor not only focus on technical requirements such as a higher speed, but also on business and marketing requirements. A few years ago HP began developing a line of PA-RISC processors to meet the needs of higher-volume and more cost-sensitive products. The article on page 43 introduces four articles that describe the latest processor in this line, the HP PA 7300LC. The HP PA 7300LC processor is optimized for entry-level to midrange high-volume systems such as workstations and servers.

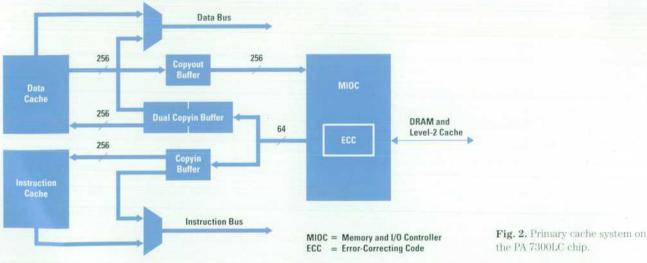

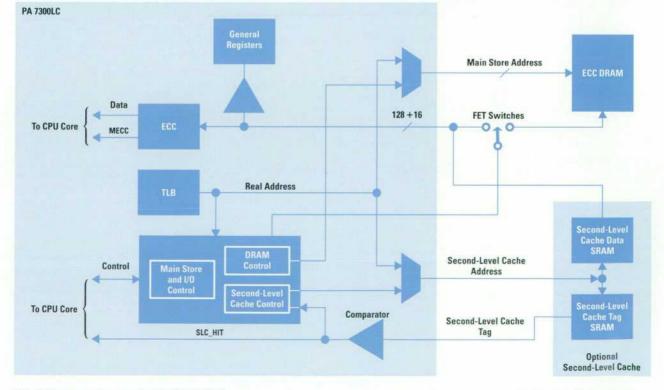

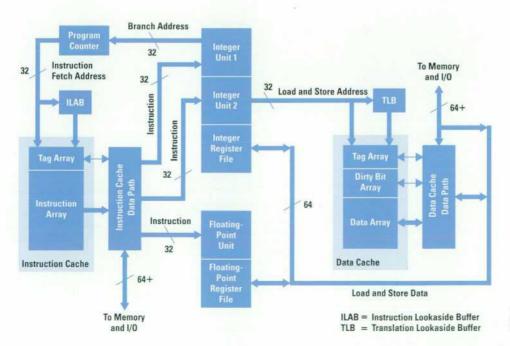

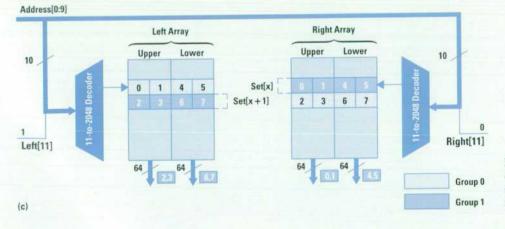

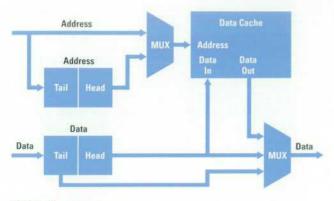

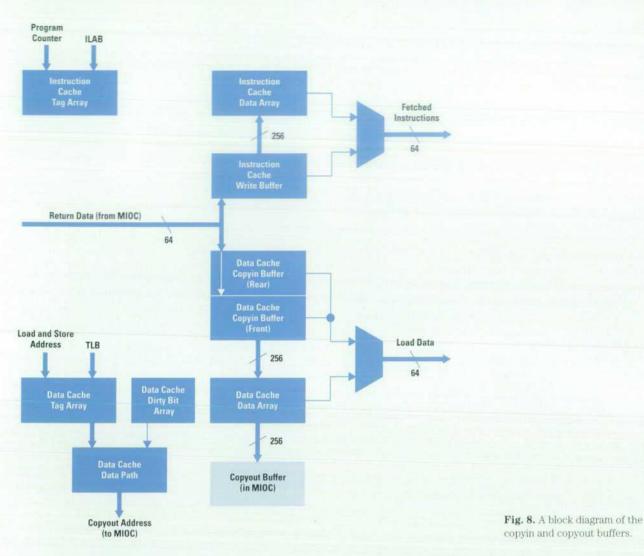

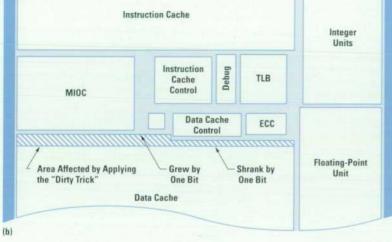

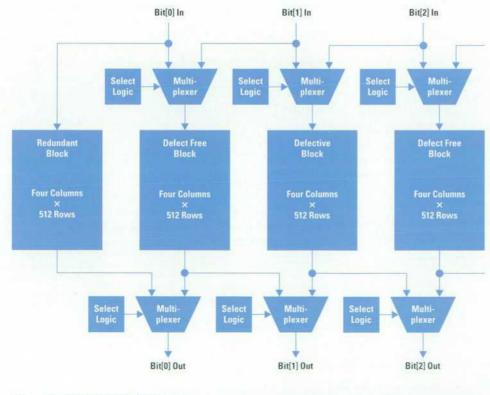

The PA 7300LC processor is the result of leveraging the superscalar CPU core from the HP PA 7100LC processor, adding a large embedded primary cache, and reducing the chip area and pipeline stalls. The article on page 48 describes the PA 7300LC microarchitecture, the CPU core, and the memory and I/O controller. The leveraging effort, the chip area reduction, and the redundant cache RAM arrays are discussed in the article on page 61.

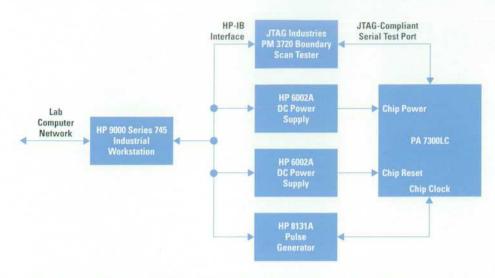

No matter how much leveraging is done or how mature the IC fabrication process, functional verification of a new chip is always an important step in the process. The article on page 69 describes the processes used in the presilicon and postsilicon phases to verify the correctness of the PA 7300LC processor.

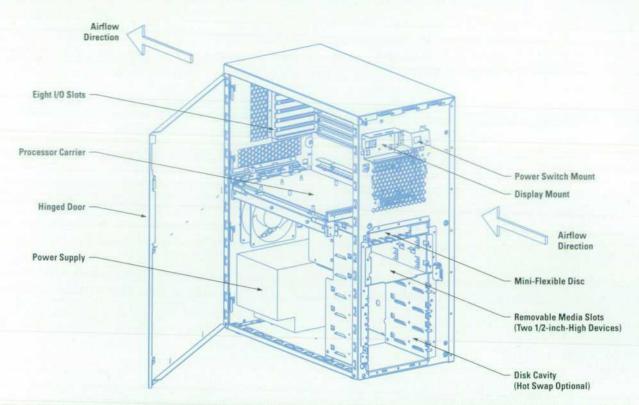

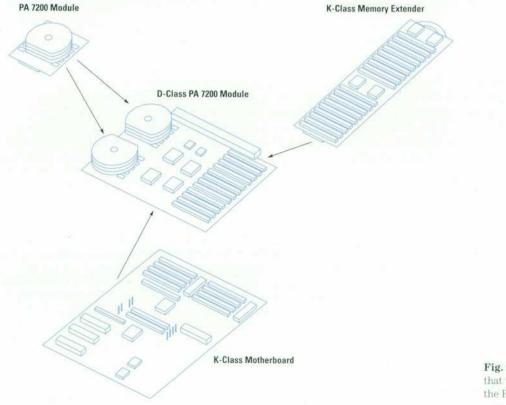

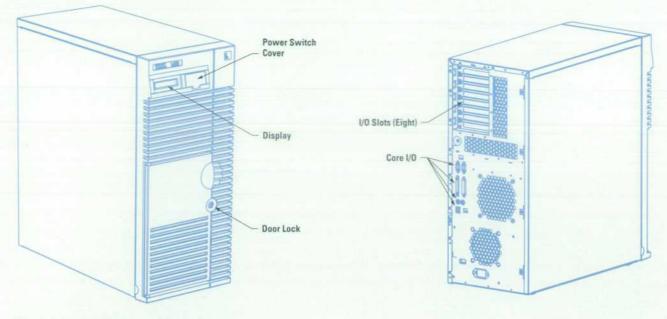

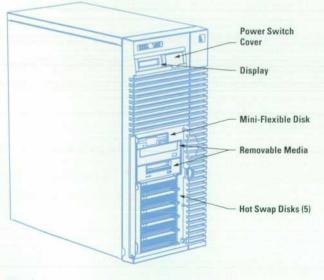

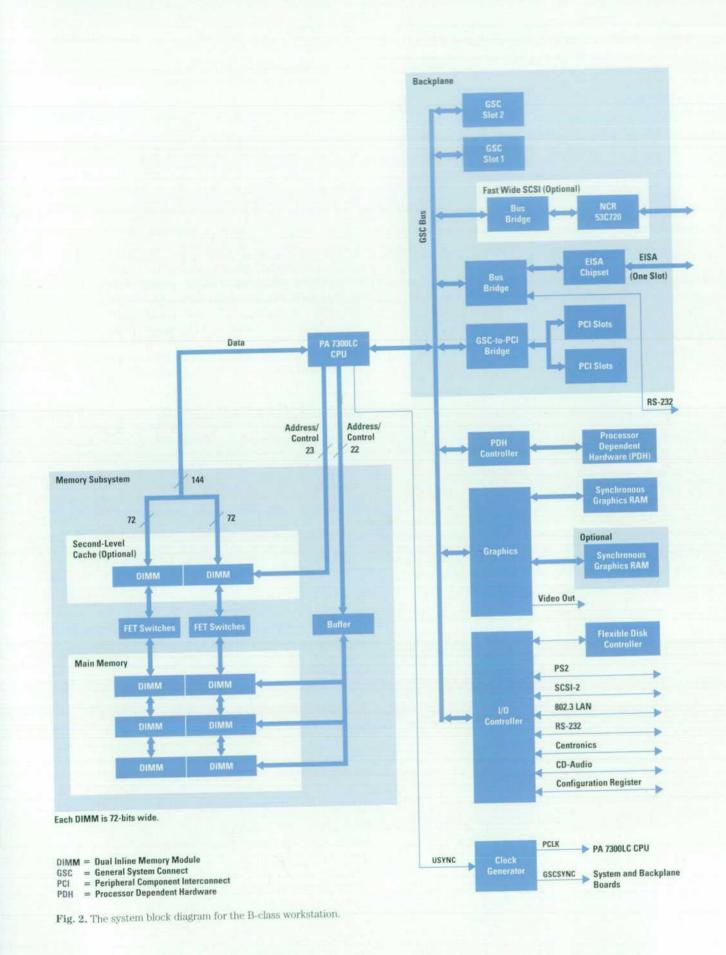

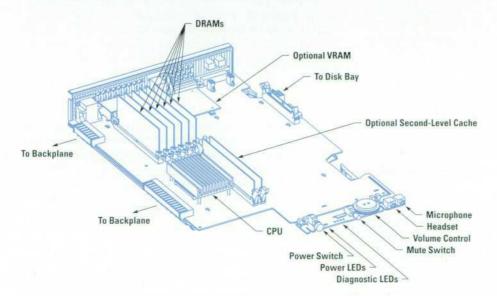

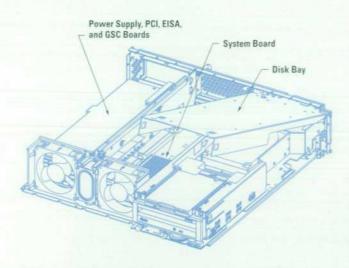

The HP 9000 D-class server (page 73) and the HP 9000 B-class workstation (page 82) are examples of products that use the PA 7300LC processor. The D-class server is targeted for the high-volume environment of departmental and branch computing. The article includes a comparison between different models of D-class servers that use HP processors other than the PA 7300LC. The HP 9000 B-class workstation is comparably priced to the HP 9000 Model 715 workstation but has superior performance and I/O capabilities. The article focuses on how cooperative engineering between the various entities involved in product development helped to reduce the time to market for this product.

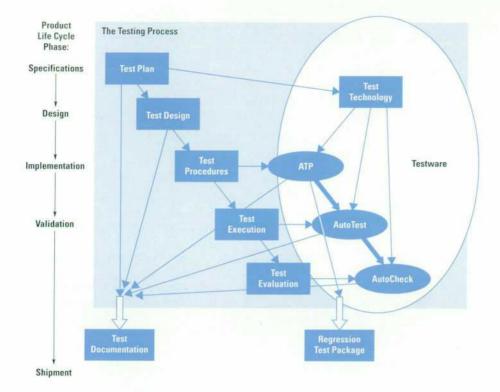

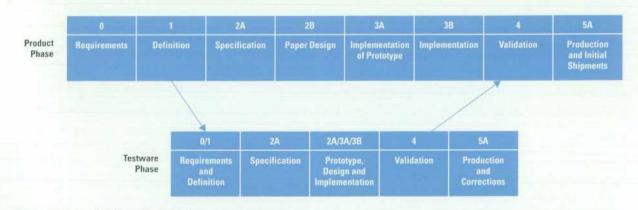

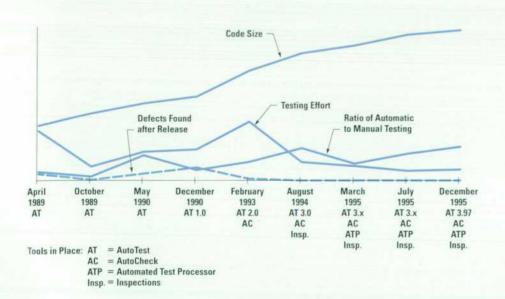

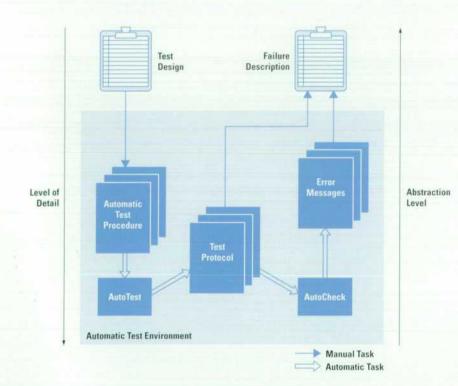

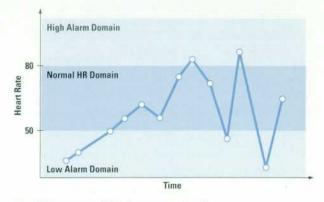

Software testing is always one of the most critical phases of the software development process. If test planning is late or inadequate, the test effort can cause late, or worse, low-quality products. The level of testing and the pass/fail criteria vary with the type of software. For example, software used in video games would not be tested the same way or have the same pass/fail criteria as software used in patient monitors. The articles beginning on page 89 describe the processes, languages, and tools the authors have developed for testing safety-critical software. In this case the safety-critical software involves software used in the HP OmniCare patient monitors, which monitor the physiological parameters of critically ill patients.

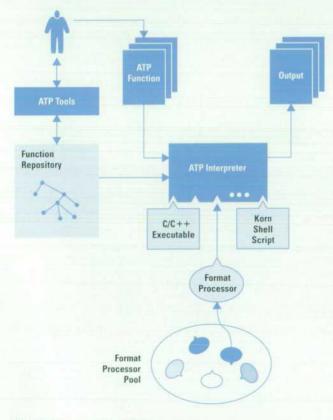

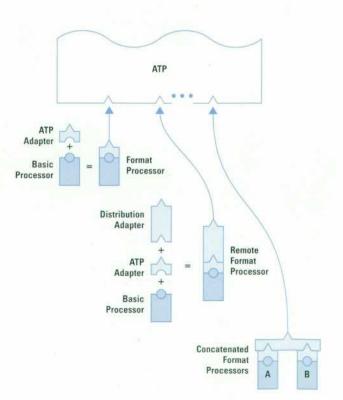

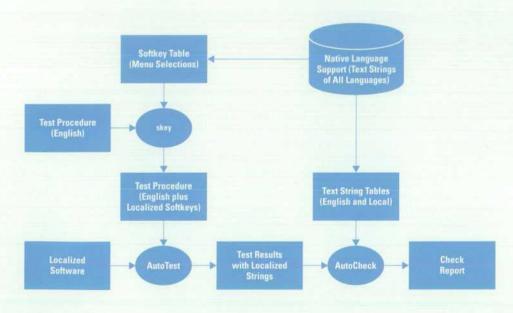

The evolution of the software testing process for the HP OmniCare patient monitors and resulting test tooling called *testware* are described in the first article. The next article (page 95) describes a high-level programming language called ATP (Automatic Test Processor), which allows the integration of existing test processors used for validation. The AutoCheck program (page 103) evaluates test files and documents the results of the evaluations. The final article (page 109) describes how these test tools can be used to help in testing localized software.

C.L. Leath Managing Editor

#### Cover

The cover shows an artistic rendition of the change in the printing model brought on by the Printing Performance Architecture (PPA) implemented in the HP DeskJet 820C. The top figure depicts printing before the PPA where most of the printing logic resides in the printer. The lower figure depicts printing after the PPA where most of the printing logic resides in the host computer.

#### What's Ahead

Featured in our August issue will be:

- The design and verification of the HP PA 8000 and PA 8200 four-way superscalar CPUs

- The HP OpenCall family of telecommunications platforms based on intelligent network concepts

- · Software to test policing in ATM networks

- An object-oriented database management system for large historical data archives

- The HP 4500 benchtop inductively coupled plasma mass spectrometer

- Five papers from the 1996 HP Design Technology Conference.

#### Reminder

Because we are getting ready for a new Journal design and focusing on other projects, we won't be publishing an issue in October.

### A Lower-Cost Inkjet Printer Based on a New Printing Performance Architecture

The HP DeskJet 820C printer is the first HP inkjet printer in an evolutionary product plan that takes advantage of computer and operating system trends to make inkjet printing affordable for more users. The printer's integrated software, firmware, and digital electronics architecture uses the computational resources in the PC instead of duplicating these resources in the printer.

#### by David J. Shelley, James T. Majewski, Mark R. Thackray, and John L. McWilliams

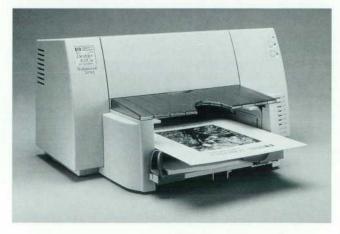

The two Hewlett-Packard divisions in Vancouver, Washington are responsible for establishing and maintaining HP color inkjet printers as market leading personal products in the home and office computing environments. These divisions have a ten-year history of successful products starting with the original HP DeskJet printer in 1986 and culminating most recently with the introduction of the new HP DeskJet 820C (Fig. 1) in the spring of 1996.

Our competitors, of course, have also been introducing products, some of which incorporate newly developed technologies that strongly challenge the performance, print quality, and cost-effectiveness of our own. It is clear that our competitors are here for the long term, so we must develop long-term strategies to compete with them.

Aside from competition, we also have before us an excellent opportunity to broaden our printing solutions to embrace the needs of the entire family, a step well beyond the traditional "take work home" professional who has been our mainstay home customer. These new customers have distinctly different needs that will require insightful understanding as well as timely incorporation of focused innovations in our products.

Fig. 1. HP DeskJet 820C color inkjet printer.

At the beginning of the HP DeskJet 820C project, it was clear that our ability to retain and grow our market leadership depended heavily upon our ability to deal with these two powerful market dynamics. We knew that we had to simultaneously stay ahead of the competition and satisfy the rapidly increasing breadth of home printing needs. The ingredients for long-term success in this endeavor were equally clear:

- Technologies that result in continuously improving print throughput and quality

- Designs that earn adequate profits at reduced customer prices

- Designs that appeal to home customers by virtue of small size, attractive industrial designs, very quiet operation, and unparalleled ease of use

- Designs capable of high-volume production at multiple international factory sites

- The ability to design products to hit narrow market windows.

We realized that no single product program could successfully satisfy all of these criteria, so we needed to develop a phased approach. We decided that each new product development effort should leverage previous capabilities while incorporating a small set of new and innovative capabilities focused on our customer needs. These new capabilities would then be leveraged forward into succeeding efforts. In this fashion we could ensure a timely series of product introductions, each building upon previous successes and incrementally providing new capabilities that would ultimately satisfy all of our strategic initiatives. In addition to the market timeliness gained by a phased approach, we also knew that this plan would use scarce development resources in the most efficient manner.

#### **Design Objectives**

The HP DeskJet 820C printer is the first product in this evolutionary product plan. In keeping with our overall strategy, the primary objectives of the development program were to:

• Leverage the speed and print quality afforded by the new writing system developed for the HP DeskJet 850C

- Leverage the printing mechanism of the HP DeskJet 850C

- Innovate by offering this printing capability at a greatly reduced price for home customers

- Introduce in the spring of 1996.

While reduced cost and a spring 1996 introduction were clearly the primary objectives for the HP DeskJet 820C effort, we also decided to begin our journey towards consumer design by making industrial design changes that fit within the constraints of a leveraged mechanism and package.

Since we had decided to leverage the writing system, print mechanism, and package, we needed to examine the electronic, firmware, and software driver subsystems to find cost reduction opportunities. Based on our initial investigation we set a program goal to reduce direct material cost by 30%.

#### **Design Approaches**

Our first design tactic recognized two trends. First, newer generations of personal computers have more than enough bandwidth to take on some of the computing load that has until now resided in the printer itself. Second, software applications are rapidly moving away from MS-DOS® and into the Microsoft Windows<sup>®</sup> environment. In view of these trends, we decided that the HP DeskJet 820C printer would not support printing from standalone DOS applications. This enabled us to develop an integrated software, firmware, and digital electronics architecture that uses the computational resources in the PC instead of duplicating these resources in the printer. We call the architecture Printing Performance Architecture, or PPA. This architectural choice enabled us to achieve half of our 30% cost reduction goal by reducing RAM from 1M bytes to 128K bytes, ROM from 2M bytes to 64K bytes, and gate count in our largest ASIC by 25%. At the same time, higher-power PCs enabled us to maintain and in many cases improve system throughput.

A second critical design decision was to disallow simultaneous firing of the black and color print cartridges during a single print swath. While this strategy achieved an additional 20% of our overall goal, the obvious risk was a reduction in throughput for documents that contain juxtaposed black and color. However, we felt that our new system architecture would mitigate this risk and still allow us to meet our performance objectives. This single decision allowed us to simplify the drive electronics for the print cartridge to the point where they could be located on a small, carriagemounted printed circuit assembly rather than on the main logic printed circuit assembly. This change, in turn, enabled two other very significant cost reductions. First, the interface between the logic and carriage printed circuit assemblies was dramatically simplified, allowing the use of standard and easily available cables and connectors rather than the custom designs that we had previously used. Second, using this new partitioning of analog functions, the design team was able to implement the required capability using two custom analog ASICs in contrast to the four that had been used in the DeskJet 850C.

An additional 10% of our cost goal was achieved by capitalizing on three cost saving opportunities in our power supply. First, the initial HP DeskJet 850 power supply was specified with significant margin to allow flexibility for the newly developed writing system in that product. However, the HP DeskJet 820C development team had the advantage of a stable writing system and therefore could specify power needs more precisely. Second, we modified the user interaction model with the printer's power functions and were able to eliminate some of the complex capabilities that were included in the HP DeskJet 850. Third, we specified our power supply at a very high level of abstraction to use the design expertise of our vendor base to deliver cost-optimal implementations.

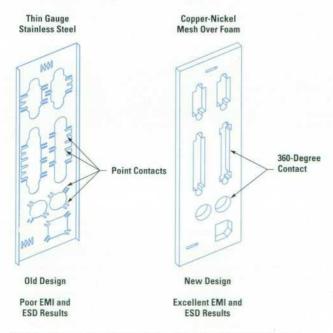

Several sources contributed to the final 20% of our cost reduction goal. Our new system architecture and new partitioning of analog functionality allowed a significant reduction in the size of our printed circuit assemblies. Direct material cost savings were realized by elimination of the connectors and support components for interconnecting to Apple PCs. Focused design work to cost-optimize our EMI and ESD solutions eliminated many discrete electronic components.

As a result of our plan to leverage and our focus on limited but meaningful innovation, the HP DeskJet 820C was introduced to the market on schedule in the spring of 1996 following a development effort that exceeded objectives by achieving a 33% direct material cost reduction and actual performance nearly twice our initial expectations. The techniques responsible for this success have been carried forward and are already incorporated into the next products in our evolutionary process.

#### **Printing Performance Architecture**

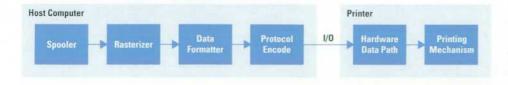

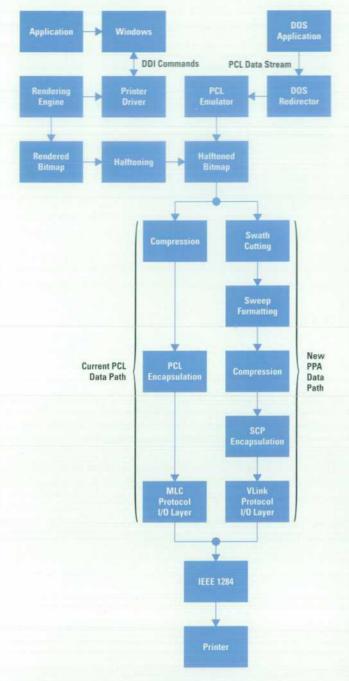

The process of printing a document created on a computer involves several steps to transform and prepare the information. In the traditional Windows model used by inkjet printers, the printer driver software receives a description of the page from the application, transforms that description into a mechanism independent format that can be understood by the printer, and encodes it into a standard printer language. The encoded description is then transferred to the printer. The printer decodes the data and formats it for its particular printing mechanism. To encode the information for transfer to the printer, Hewlett-Packard developed a standard language called PCL (Printer Control Language). Because of the widespread use of HP printers, this language has become a de facto standard. PCL allows the computer to prepare an image for printing without detailed knowledge of the mechanical details of the printer.

For the Microsoft Windows environment, HP has always developed the software drivers for its inkjet printers. In the Windows model, the application sends a page description to the driver through the operating system. The description is in the form of drawing objects (lines, rectangles, text, etc.). The driver then rasterizes the description. Rasterization is the process of mapping the page description to an X-Y plane or bitmap. At this point, the data still must undergo several more transformations before it can be used to print. For example, the first bitmap may be 24-bit data at 300 dpi, whereas the inkjet mechanism may be 600 dpi and only able to put one of four colors at each pixel (black; cyan, magenta, yellow). Traditionally, the driver performed some of the needed transformations, but left many of the more compute-intensive ones to dedicated hardware and firmware in the printer.

After the driver has performed all of its computations, it encodes the information using the subset of PCL needed for bitmapped data. The printer in turn decodes the PCL and

Fig. 2. Traditional PCL printing model.

performs all of the necessary further computations to format the data for the printing mechanism. Manipulations the printer must perform include, but are not limited to, some color transformations, cutting the data into individual swaths, and separating the data into columns (inkjet cartridges are composed of two columns of staggered nozzles). This process is diagrammed in Fig. 2.

The process in the MS-DOS environment is similar with two exceptions. One, the application must perform the rasterization for all graphics and PCL encoding, and two, the printer will accept nonrasterized text, alleviating the need for the application to do it. Because of this second difference, previous inkjet printers were required to have extensive memoryintensive fonts built into them. In addition, the printer had to contain firmware and hardware to rasterize the fonts. Since the data manipulations performed were extensive, they required a powerful microprocessor and significant amounts of dedicated hardware.

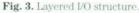

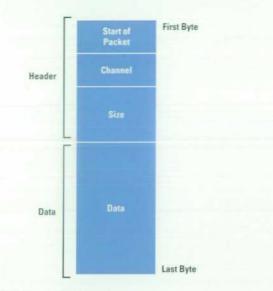

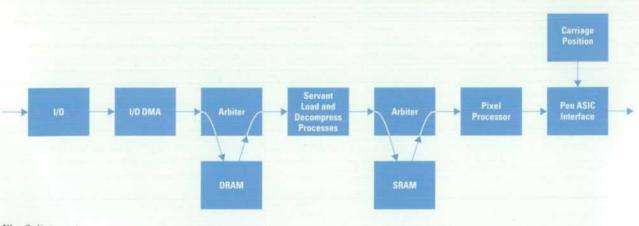

The concept of the new Printing Performance Architecture, or PPA, is to change this model by eliminating some of the steps. Because modern personal computers have powerful microprocessors and a large amount of system memory, the task of data formatting for the print mechanism is moved entirely to the host computer. Also, because the data is no longer in a PCL-compatible format, PCL is not used to transmit the data to the printer. Instead, a very simple proprietary protocol was developed. The protocol is simple enough that the hardware can automatically depacketize the data without help from the firmware. The data is then directly used to print the image on the page. This process is diagrammed in Fig. 3.

#### Advantages of PPA

The primary advantages of PPA are cost and performance. A PPA printer can deliver performance similar to a traditional non-PPA printer at a reduced cost. Alternatively, it can deliver higher levels of performance at a similar cost. The reasons for the cost advantage fall into two areas: less memory is required (both RAM and ROM), and a lower-performance microprocessor can be used in the printer because the microprocessor doesn't have to touch the data.

Memory costs are a significant portion of the material cost of a low-end printer. A PPA printer requires significantly less ROM and RAM. First, the PPA printer doesn't have to store any internal fonts. Traditional printers supported both the Windows environment and the DOS environment. The printing model in the DOS environment requires the printer to store font information. A DOS application sends an ASCII code for the desired text character. To print that character, the printer needs a bitmap for that character in its ROM. In contrast, applications in the Windows environment send only bitmapped graphic information to the printer, never ASCII text. Because the PPA printer is designed exclusively for the Windows environment, it doesn't need to store the fonts in ROM.

Second, because the printer doesn't do any PCL decoding, swath cutting, or data formatting, the printer requires much less firmware, again saving ROM. The primary functions of the printer firmware are mechanism control, input/output, and the user interface. In the HP DeskJet 820C, the firmware is stored in only 64K bytes of ROM. Because there is so little, it was possible to integrate the ROM into the digital ASIC. Previous non-PPA printers of similar capability used 512K bytes or more of ROM.

Finally, because the processor doesn't touch the data and doesn't need to create any intermediate forms of the image data, the printer requires less RAM. The HP DeskJet 820C uses a 128K-byte DRAM. The previous generation, non-PPA printer used 512K to 1M bytes of RAM. Because there are fewer memory ICs, the memory cost for a PPA printer is much lower. The reduced number of memory devices also reduces the printed circuit board area, again saving cost.

The second factor in saving cost comes from the need for less microprocessor horsepower. In a PPA printer, the processor does not do swath cutting and formatting of the data. Its primary functions are mechanism control, input/output, and the user interface. This requires a less complex and consequently less expensive microprocessor. The HP DeskJet 820C uses a Motorola 68EC000. The 68EC000 can be configured with either an 8-bit or a 16-bit data bus. In the HP Desk-Jet 820C, the processor is used in 8-bit mode. This reduces the bus width in the digital custom ASIC, again saving area and hence cost.

Finally, because of the simplified data path in the printer (the data path is the path the data takes from the input/output port, through the ASIC, and out to the print cartridge), it was possible in the HP DeskJet 820C to design a data path in which the processor doesn't touch the image data. A dedicated hardware data path is always much faster, albeit less flexible, than a data path in which the processor must transform or handle the data. A full hardware data path is not limited to a PPA architecture, but is much easier to accomplish in a PPA printer because of the simplified data path.

Fig. 3. New Printing Performance Architecture (PPA) printing model.

#### Challenges of PPA

While PPA has some significant advantages, it also brings with it some challenges:

- DOS is supported only through Windows and not in a standalone environment.

- PPA hosts must be more powerful than hosts for an equivalent non-PPA printer.

- The printer driver requires detailed knowledge of the printing mechanism.

- PPA required a change in the development and manufacturing paradigm at the HP Vancouver Division.

The PPA architecture does not support printing in the traditional standalone DOS environment. In the Windows environment, all information sent to the printer is bitmapped graphics. The data is prepared under the control of a single, HP-designed and optimized printer driver. In the older DOS environment, application vendors write their own printer drivers. Applications send ASCII codes to the printer and expect the printer to use its own internal fonts to generate the bitmapped characters. The applications have no knowledge of the printing mechanism and hence are unable to do any swath cutting or data formatting.

The HP DeskJet 820C does support printing from a DOS application if the application is run under the Windows environment. Windows allows DOS-only applications to be run in a *DOS box*. Printing in this environment uses the standard Windows printing mechanism and hence the HP driver.

PPA printers require a higher-powered host than non-PPA printers to achieve comparable levels of performance. Because the job of swath cutting and data formatting is now done by the PC, more computing power is required. On the HP DeskJet 820C, acceptable levels of performance are achieved with a 66-MHz Intel486-based machine with 8M bytes of RAM.

PPA required a shift in the HP Vancouver Division's development and manufacturing paradigm. Having designed and built PCL-based printers for over 15 years, all of the division's tools and processes were centered around this type of printer. For instance, over the years the manufacturing and customer assurance organizations had developed many tools based around PCL printers for doing production tests and exercising the printer in environmental tests. None of these tools work with a PPA printer. Similarly, the firmware test organization had to revise its tests completely. Because the HP DeskJet 820C printer has only 64K bytes of ROM, extensive demo pages and self-test pages could no longer be included in the printer.

Because of the high level of integration and because the architecture follows the paradigm that "the processor doesn't touch the dots," it is difficult to observe the flow of data through the machine. This made debugging problems during development quite challenging. This problem was solved in several steps. First, the ASIC design team did extensive simulations. Second, the team used a hardware emulator to emulate the digital ASIC. This emulator had a mechanism that provided ports to internal nodes so that they could be observed with a logic analyzer. Finally, simple patterns were devised and sent through the architecture that simplified problems and made debugging possible. Finally, in the PPA environment, the driver must have knowledge of the printing hardware. This makes the driver less universal and the job of leveraging the driver to future products more difficult. The driver was carefully organized and modularized so the hardware dependent pieces can be changed while the underlying driver features can be leveraged into future products.

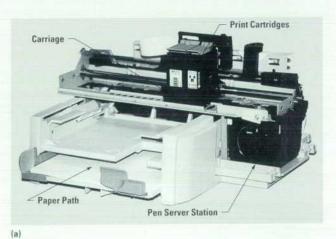

#### Inside the Printer

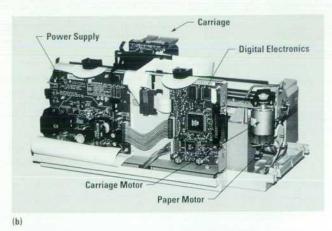

Inkjet printing is a complicated process that involves tying together several electromechanical subsystems that work together to create the printed page. All inkjet printers consist of these major subsystems regardless of the particular implementation used for each one. Fig. 4 shows the HP DeskJet 820C printer with its top cover removed and the major subsystems labeled.

**Paper Path.** The paper path is responsible for moving paper through the printer. The user inserts paper or envelopes into the input tray. At the appropriate time, a single piece of paper is picked from the stack and begins moving through the printer. Each time the carriage finishes a pass over the paper, the paper is advanced an appropriate amount to prepare for the next pass of the carriage. At the end of a page, the paper is "kicked," or deposited in the output tray, where the user can remove it. In the HP DeskJet S20C, a single electric motor is used to move the paper. Paper movement is open-loop—there is no feedback about the actual paper

Fig. 4. HP DeskJet 820C printer subsystems.

position. The paper path in the HP DeskJet 820C gracefully handles a variety of paper sizes and thicknesses as well as envelopes.

Carriage. The carriage holds the pens used in the printer. To print a swath of data, the printer moves the carriage across the page at a constant speed, firing the pens at appropriate times. A single motor is used to move the carriage. Carriage movement is a closed-loop process. The carriage's position is tracked using an LED, which shines on a photoreceptor and a strip of plastic made up of alternating light and dark regions placed between the LED and the photoreceptor. As the carriage moves across the page, logic recognizes when the LED is in front of a dark region and when it is in front of a transparent region. Using this information, it tracks the carriage's position on the page. In addition to holding the pens, the carriage holds a printed circuit board. On the board are parts that connect electrically to the pens and a portion of the electronics needed to drive the pens. In the HP DeskJet 820C, all electronics directly used to fire the pens are located on the carriage board (see article, page 38).

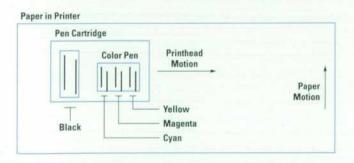

Print Cartridges. The print cartridges in the HP DeskJet 820C are user-replaceable cartridges that contain both the ink and the mechanism for placing the ink on the paper (thermal inkjet). They are often referred to simply as the "pens." The pens are the same as those used in the HP DeskJet 850 and 870 printers. There are two pens: a black pen and a color pen. The black pen has 300 nozzles spaced at 1/600 inch. The swath height for black is therefore 1/2 inch. The color pen holds three colors of ink: cyan, magenta, and yellow. Each color is printed with a series of 64 nozzles spaced at 1/300 inch. The swath height is therefore approximately 1/5 inch. Colors other than cyan, magenta, and yellow are created by placing dots of these three colors in close proximity in appropriate ratios. Since at a distance of more than a few inches the resolution of the eye is not great enough to discern the individual dots, they blend together visually, forming the desired colors.

**Pen Service Station**. To maximize the life of the pens and to maintain optimum print quality over that life, it is necessary to service the pens. Servicing includes but is not limited to such actions as capping the pens when not printing so that they do not dry out and wiping them on occasion to prevent ink buildup. The service station includes all the electrical and mechanical parts necessary to perform the servicing actions. In particular, it includes a motor that is used to actuate actions such as wiping and capping. The motor is controlled by an open-loop process.

**Power Supply**. A power supply is needed to provide energy to the printer. The power supply accepts an ac signal from a standard outlet and converts it to the dc voltages and currents used to power the printer. Because the HP DeskJet 820C will be sold worldwide, it is capable of running on all permutations of 50/60Hz and 110/220V inputs found around the world.

**Digital Electronics.** The digital electronics are responsible for controlling all of the other electromechanical parts. The digital electronics generally include at least one of each of the following: a microprocessor, a ROM, a DRAM or SRAM or both, a block of custom logic, and an EEPROM. The microprocessor controls all mechanism movements, I/O, the user interface, and print data manipulation if necessary. The ROM holds firmware, and in previous products but not in the HP DeskJet 820C, fonts. The volatile memory is used to hold firmware variables and print data and commands that arrive over the I/O port. The custom logic implements printer-specific functions that require hardware support. The EEPROM holds information that must be retained through a power cycle. In the HP DeskJet 820C, the microprocessor, the ROM, the custom logic, and an SRAM are all integrated into a single ASIC (see articles, pages 22 and 31).

**Case**. The case is the part of the printer that the customer sees, so every effort is made to make it attractive. The case includes a small panel of LEDs and buttons by means of which the user interacts with the printer. The front panel of the HP DeskJet 820C is very simple, consisting of just two buttons and three LEDs. The case also has a door that can be lifted to gain access to the pens.

**Driver.** In addition to the physical part of the printer, all printer products require a software driver, which resides on the host computer. The driver allows applications software running on the PC to interact with the printer. In most modern operating systems, an application that wishes to print calls the printer driver through the operating system. This model allows the printer manufacturer to supply the driver, so application suppliers don't have to. The exception to this model is DOS, which requires the driver be integrated into the application. Because of the simplifications that can be made to the printer, the HP DeskJet 820C only works with Windows applications, or DOS applications running in a DOS box (see above and the article on page 12).

#### HP DeskJet 820C Printing Sequence

To begin the printing sequence, the user chooses Print from the appropriate menu in the application. The application formats the page into the standard description format used by the Windows operating system. Using this format, the application passes a description of the page to the printer driver. The driver reformats the page into a form appropriate for sending to the printer. In the process of reformatting the image, the driver performs various transformations to map the image to the inkjet printing technology. In previous HP inkjet printers, the format used to send data to the printer was PCL, a page description language. In the HP DeskJet 820C, the format is a bitmapped image that can be used to fire the printheads with minimal further transformations.

Once the image is in the right format, data is sent to the printer over the I/O cable. Before the data can be printed, the driver must send commands to the printer that tell it to prepare to print a page. When the driver sends these commands, the printer first uncaps the pens and services them to prepare them for printing. Then it picks a piece of paper and advances it to the first spot where printing will occur.

After the printer is prepared and has enough data in its local memory to print an entire swath, it performs a print sweep by moving the carriage across the page. As it moves the carriage, it pulls data out of its local memory, performs some final formatting, and uses the data to fire the printheads at appropriate times. After the sweep has been completed, the printer advances the paper, waits for enough data to print the next swath to arrive over the I/O, and then, upon command from the driver, prints the data. The process repeats for the rest of the page. At end of the page, again upon command from the driver, the printer kicks the paper, depositing it in the output tray. Assuming that there are no further pages to be printed, the printer then parks the carriage over the service station, caps the pens, and performs other cleanup pen servicing. The printer then waits patiently until the next time it is called upon to print.

#### Summary

The advance of personal computer horsepower and the uniformity of the Windows printing environment in which HP has control of the printer driver have made it possible to change from the PCL printer model to a PPA printer model. The customer benefit is that PPA printers can provide equivalent levels of performance at a much lower cost.

Microsoft, Windows, and MS-DOS are U.S. registered trademarks of Microsoft Corporation. Intel486 is a U.S. trademark of Intel Corporation.

### **PPA Printer Software Driver Design**

The software driver for the HP DeskJet 820C printer performs many functions that were formerly performed in the printer, including swath cutting, data formatting, and communications. The driver also includes a PCL emulation module for DOS application support.

### by David M. Hall, Lee W. Jackson, Katrina Heiles, Karen E. Van der Veer, and Thomas J. Halpenny

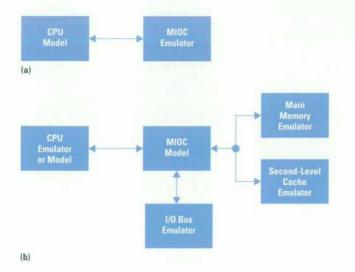

The software driver for the new HP DeskJet 820C printer includes many new functions that need to be performed on the host computer because of the printer's Printing Performance Architecture (PPA). In older PCL (Printer Control Language) printers, these functions were performed in the printer. Fig. 1 shows the differences. These functions include:

- Swath cutting

- Data formatting

- PPA communications

- PCL emulation for DOS application support.

This article provides an overview of the changes necessary for supporting PPA and then discusses each of the functions listed above in more detail.

#### **Driver Overview**

Under the Windows<sup>®</sup> operating system, printer drivers are responsible for supporting a specific API (application programming interface) known as the DDI (Device Driver Interface). This interface gives the driver fairly high-level drawing commands. It is up to the driver to take those commands and produce a bitmap that can be encapsulated in a language and sent to the printer.

Typically, within a Windows printer driver, a rendering engine takes the DDI commands and produces a rendered bitmap. A halftoning algorithm is performed on the rendered bitmap and a halftoned bitmap is produced. This halftoned bitmap is typically in a format that can be encapsulated in a language such as PCL and then given to the printer.

For the HP DeskJet 820C, this halftoned bitmap has to be put through additional processing as shown in Fig. 1 to create data that is ready to be printed by the printer's electronics directly. This additional processing includes swath cutting and sweep formatting.

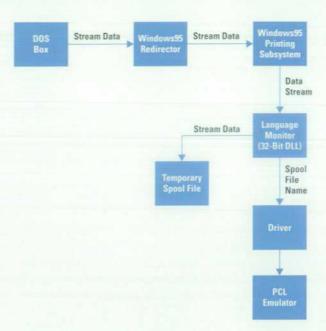

Since the HP DeskJet 820C does not understand PCL (Printer Control Language), a PCL emulation module is necessary to provide support for DOS applications. The DOS application data stream is captured by a DOS redirector and passed to the PCL emulator, which produces a halftoned bitmap ready for swath cutting.

#### PCL versus PPA

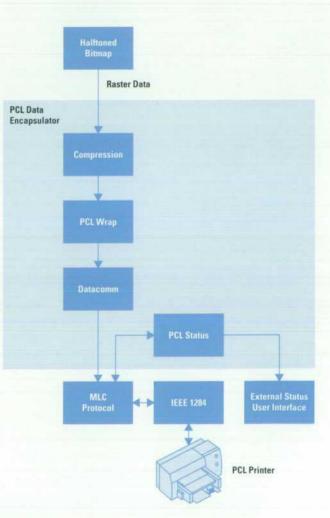

Fig. 2 shows the printing model for PCL printers. For PCL printers, the process of encapsulating the halftoned bitmap

is fairly straightforward. Raster data from the halftoned bitmap is compressed, PCL wrapped, and then sent to the I/O module. The reason that this is a simple process is that PCL printers are designed to receive data in the same format as the halftoned bitmap. PCL printers unwrap the data into an internal buffer and perform the necessary swath cutting and data formatting internally.

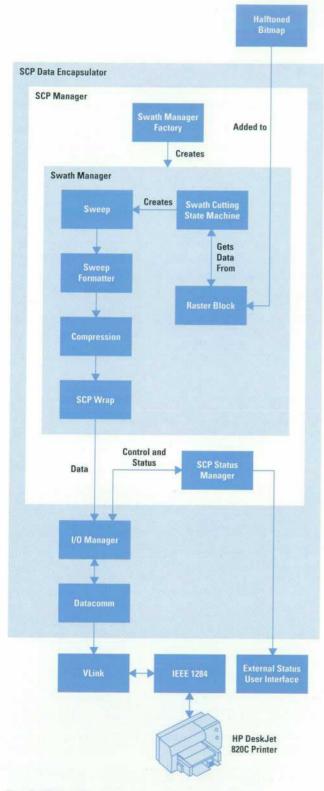

Fig. 3 shows the printing model for PPA printers. For the HP DeskJet 820C, the PCL encapsulator is replaced with an SCP data encapsulator. SCP (Sleek Command Protocol) is an HP-proprietary command language. This module contains swath cutting functionality, data formatting, SCP language encapsulation, and printer status management.

Raster data from the halftoned bitmap comes into the SCP data encapsulator, goes through the SCP manager, and eventually arrives at a raster block within the swath manager. The swath cutting state machine examines the data and determines the appropriate sweep to generate. A sweep is a collection of rasters appropriate for the printer mechanism to print while it sweeps the printhead over the paper.

Once the sweep is generated, it is given to the sweep formatter. The sweep formatter is responsible for taking the sweep data and putting it into the appropriate format for the HP DeskJet 820C internal hardware. Then the data is compressed, wrapped in SCP, and handed off to the I/O layer.

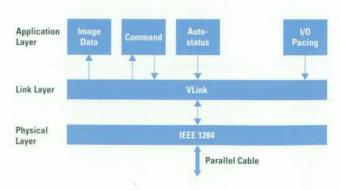

The I/O layer is responsible for communicating with the printer by wrapping the data stream in VLink and IEEE 1284 protocols. VLink is an HP-proprietary link-level protocol and IEEE 1284 is an industry-standard physical-layer protocol.

#### Performing Swath Cutting on the Host

Swath cutting is the process of taking a page of halftoned raster data and producing sweep data appropriate for the carriage electronics to print as the printhead is sweeping across the page. Swath cutting has historically been part of printer firmware, but in the HP DeskJet 820C printer, it is part of the software driver running on the host computer. Typically, a swath manager encapsulates a swath cutting engine and receives as input a bitmap representation of the page to be printed. The swath manager is responsible for determining how the pens and paper should be moved and when and how the pens should be fired to produce the printed page. The swath manager must balance the often conflicting goals of printing with the highest possible print

Fig. 1. Printer driver functional block diagram, showing differences between PCL and PPA data paths.

quality and printing as fast as possible. The swath manager must be aware of certain printer-specific attributes such as printhead alignment and strategies to minimize line feed error. In PPA, swath management is performed on the host computer.

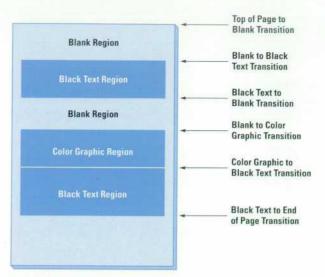

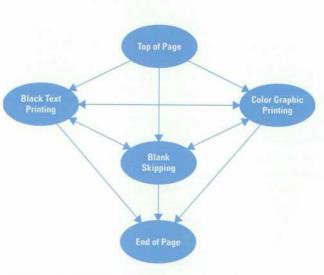

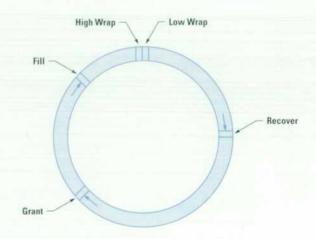

The process of swath cutting can be readily modeled using a state machine. Consider the example shown in Fig. 4. A state machine capable of processing this page would need to contain five states: Top of Page, Blank Skipping, Black Text Printing, Color Graphic Printing, and End of Page. Thus, we can create the state machine shown in Fig. 5. A particular instance of a state machine exists for each print mode the swath manager supports. For example, there could be a print mode for pages that only have black text on them, another print mode for pages with black and color, and yet another print mode for pages with complex graphic images.

As the state machine begins to examine the data on the page, it starts in the Top of Page state. The first data it comes to is a series of blanks. This would cause it to move to the Blank Skipping state. During this transition the swath manager would typically load the page. While in the Blank Skipping state, the swath manager would advance the paper. Next, it would encounter a black text region and move to the Black Text Printing state. Depending upon the type of printing being done at that time, this transition may produce a sweep.

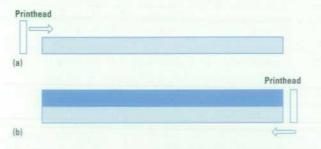

Assume that for this print mode, the data on the page is being printed by making two sweeps for each line. Thus, in making the transition from Blank Skipping to Black Text Printing the printer could print the first pass of the black text region with the bottom half of the printhead, advance the paper half a printhead height, and then enter the Black Text Printing state. During the next sweep generated, the Black Text Printing state would finish the lines that were printed during the transition and continue printing the black text region (see Fig. 6). The data on the page would continue to be consumed and transitions made between states until the End of Page state is reached.

Fig. 2. PCL printing model.

Fig. 4. Swath cutting state machine transitions for a typical page.

#### **PPA Data Formatting**

The HP DeskJet 820's Printer Performance Architecture requires the host to perform the majority of the data manipulation. The data that is sent to the printer must be in a format that is very close to the final form used to fire the printheads. The main difficulty in formatting the data for the printhead lies in the fact that the data doesn't come out of one position on the carriage mechanism. Instead, there are two columns for each of the four pen colors. Each column is at a different vertical and horizontal offset from a relative zero carriage position. To minimize the cost and complexity of the electronics in the printer mechanism, the data sent from the host to the printer must be ordered so that it is ready to go directly into these offset printheads in the appropriate order so that it is fired at the correct locations on the page. This ordering is based on:

- The starting page position of each color

- The *servant* architecture in the printer hardware (described later)

- The printhead (see Fig. 7).

Fig. 5. Swath cutting state machine.

Fig. 3. PPA printing model.

Obviously, this example is a simple one. The number of states and the number of transitions to consume data for a real page can be quite large. Using PPA we have the opportunity to perform the resource-intensive task of swath cutting on the host. This allows greater flexibility in developing machines with unique print modes, which provides the opportunity for higher print quality and throughput as well as reduced mechanism costs.

Fig. 6. (a) In making the transition from Blank Skipping to Black Text Printing, the printer prints the first pass of the black text region with the bottom half of the printhead, advances the paper half a printhead height, and then enters the Black Text Printing state. (b) During the next sweep generated, the Black Text Printing state finishes the lines that were printed during the transition and continues printing the black text region.

To print a page, it is necessary for the carriage mechanism to move back and forth across the page, firing drops of ink as it moves. Each movement of the carriage across the page is called a print sweep. When the driver receives a page to print from some application, it renders the page into a halftoned bitmap. At this point, a PCL printer driver would send compressed and encapsulated PCL data directly to the printer. The PPA printer driver uses the swath cutting state machine to generate a swath of data that can be printed by a single pass of the pen carriage. The resulting swath of data is passed on to the sweep formatter, which manipulates the data into a buffer that can be copied directly to the printheads. The print sweep formatter uses knowledge of the pen carriage, hardware, and firmware architecture to prepare and reformat the data into a print sweep.

The number of print sweeps required on a given page is dependent upon:

- The amount of data on the page (text or dense graphics)

- The print mode selected by the user (best, normal, or econofast)

- The paper type (plain, glossy, transparency, or special).

For each print sweep, the host sends two pieces of information to the printer. The first is the PRINT\_SWEEP data, a buffer of image data sent before the PRINT\_SWEEP command, which contains an entire sweep of swing buffer data blocks in the correct order. The second piece of information is the PRINT\_SWEEP command, the mechanism by which the driver tells the printer where and how to place the print sweep data on the page. A PRINT\_SWEEP command contains minimum and maximum positions for each pen column, the

Fig. 7. HP DeskJet 820C print cartridge layout. The lines correspond to nozzle columns and their general configuration on the printer carriage. print direction, print speeds, and NEXT\_PRINT\_SWEEP information.

The PRINT\_SWEEP command information is calculated by the printer driver based upon:

- Which pens are active (black, cyan, magenta, yellow)

- The starting and ending locations on the page for each pen color

- The direction of the print sweep

- The servant architecture:

- The distances between pens

- The distances between odd and even columns within a pen

- The 0,0 position in relation to the pen columns.

#### Servant Architecture

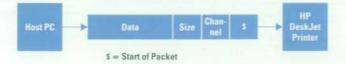

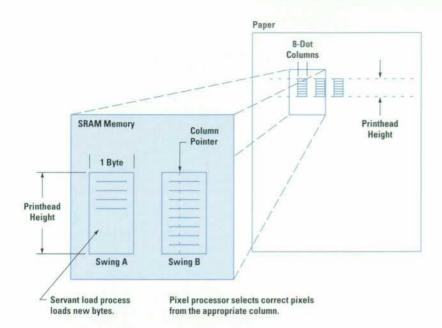

The servant hardware (see article, page 31) is composed of a pair of buffers, called *swing buffers*, for each column of the printhead (two columns per color). To build a print sweep, the driver must:

- Separate the image into CMY planes, or primitive data blocks

- Separate the primitive data blocks into swing buffer data blocks

- Order the swing buffer data blocks into a servant image.

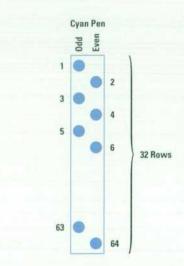

A primitive data block (a bitmap image of each plane for each color) is created by the driver. Each primitive data block needs to be split into two separate swing buffer data blocks: an odd block and an even block. This is necessary because of the pen design, which consists of two offset columns, as pictured in Fig. 8.

Each column on the color pen has 32 nozzles. The color pen has a height of 64/300 inch. For any given column of data, rows 1, 3, 5, ..., 63 will be part of the odd column and rows 2, 4, 6, ..., 64 will be part of the even column.

The even and odd swing buffer data blocks are each 8 bits wide, the width of servant RAM, and each is the height of a printhead nozzle column. Swing buffer data blocks are cut for each primitive color and for either the even or odd nozzle column. Thus, each swing buffer data block contains every other row from the primitive data block.

Fig. 8. Each color pen has two offset columns of nozzles.

| Byte 0 | Byte 1 | Byte 2 | Byte 3 | Byte 4 | Byte 5 |

|--------|--------|--------|--------|--------|--------|

| 0      | 1      | 2      | 3      | 4      | 5      |

| 6      | 7      | 8      | 9      | 10     | 11     |

| 12     | 13     | 14     | 15     | 18     | 17     |

| 18     | 19     | 20     | 21     | 22     | 23     |

| 24     | 25     | 26     | 27     | 28     | 29     |

| 30     | 31     | 32     | 33     | 34     | 35     |

| 36     | 37     | 38     | 39     | 40     | 41     |

| 42     | 43     | 44     | 45     | 46     | 47     |

| 48     | 49     | 50     | 51     | 52     | 53     |

| 54     | 55     | 56     | 57     | 58     | 59     |

| 60     | 61     | 62     | 63     | 64     | 65     |

| 66     | 67     | 68     | 69     | 70     | 71     |

| 72     | 73     | 74     | 75     | 76     | 77     |

| 78     | 79     | 80     | 81     | 82     | 83     |

| 84     | 85     | 86     | 87     | 88     | 89     |

| •      | •      | •      | •      | •      | •      |

| •      | •      | •      | •      | •      | •      |

| •      | •      | •      |        | •      | •      |

| 120    | 121    | 122    | 123    | 124    | 125    |

Fig. 9. Primitive data block organization for a printhead that has two columns of six nozzles per color. Byte n (n=0, 1, 2, 3, 4, 5) is a buffer of data 8 pixels wide by 6 rows (nozzles) high. The HP DeskJet 820C printheads have two 32-nozzle columns per color, as shown in Fig. 8.

Fig. 9 shows a simplified example of a primitive data block. Each byte is a buffer of data that is one byte (8 pixels) wide by N rows high, where N is the number of nozzles in a printhead column. For the example in Fig. 9, N is 6, while N is 32 for the HP DeskJet 820C color printheads.

Each column of the primitive data block in Fig. 9 is divided into four swing buffer data blocks with bytes relocated to the positions shown in Fig. 10. Only the cyan pen is shown, and only two of the swing buffer data blocks for each column of Fig. 9 are shown. The drawing would be similar for the magenta and yellow pens.

Once the data is in the form of even and odd swing buffer data blocks, the blocks must be ordered and sent to the printer. This ordering is done with knowledge of the column spacing on the printhead and knowledge of the order in which the servant architecture will require the data. The printer driver controls the order in which the columns will trigger via fields in the PRINT\_SWEEP command. The ordered swing buffer data blocks are then sent down as PRINT\_SWEEP data ready to be loaded into the primitive swing buffers in the printhead.

CC:x = Cyan Odd Printhead Column: Primitive Data Block # CE:x = Cyan Even Printhead Column: Primitive Data Block #

Fig. 10. Swing buffer data blocks for the example primitive data block shown in Fig. 9.

Each primitive swing buffer consists of two 8-bit columns, separated by a *swing trigger point*. While the servant print process is unloading one side of the odd column swing buffer, the other side of the odd column swing buffer is being loaded by the servant load process. Once the byte is loaded, the servant print process fires one bit by 32 rows at a time for each pen column in the color pen. When the servant print process has unloaded all eight bits, it crosses a swing trigger point, and the servant print process switches to the other swing buffer and triggers the servant load process to load the empty swing buffer. The pen fires one bit by 32 rows at a time for any complexity involved below the byte level.

When all of the swing buffer data blocks have been consumed by the printhead, the carriage mechanism uses the NEXT\_PRINT\_SWEEP information to position itself for the start of the next print sweep.

Because the PPA printer relies upon the driver to format the data appropriately, the architecture does not require the printer firmware to have any knowledge of the operations just described. Thus, the cost and complexity of the electronics in the printer mechanism are significantly reduced.

#### **PPA** Communication

One of the goals of the HP DeskJet 820C printer is to provide continuous feedback to the user during any printing operation, and to guide the user during problem solving. To accomplish this, the driver requires a mechanism to ask the printer for information and to allow the printer to notify the driver whenever something happens (the printer is out of paper, the user opened the cover, etc.). The mechanism used by the PPA driver to communicate with the printer is called *status messaging*.

To notify the user to align the print cartridges when a print cartridge has been changed, that the top cover is open, or that something else needs attention, a bidirectional link with the printer is required. Two new HP-proprietary protocols allow the driver to communicate bidirectionally with the HP DeskJet 820C: VLink packet protocol and Sleek Command Protocol (SCP). Previous HP DeskJet printers used an I/O packetizing protocol called MLC (Multiple Logical Channel) and a proprietary HP printer command protocol. For PPA, VLink replaces MLC, and SCP replaces both PCL and the old printer command protocol.

While giving users error messages might seem to be a luxury they could do without, the real reason to have a protocol like VLink is that it is useful to figure out what is wrong when, for example, the printer's input buffer fills up, the printer stops accepting data, and the host is unable to send even one more byte. This often happens and is temporary, but in the days before bidirectional protocols, the driver would sometimes wait and wait to be allowed to send again, and it didn't know whether the delay was because the top cover had been opened, a print cartridge had failed, or a fatal error had occurred. It is helpful to know whether to abort the job or ask the user to insert a print cartridge or close the door. With a bidirectional protocol, the printer tells the driver exactly what the problem is, and the driver can decide what action to take next.

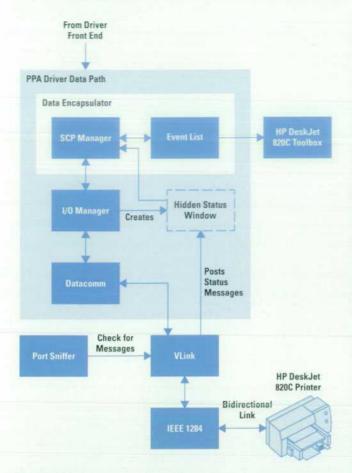

Fig. 11. PPA status messaging architecture.

A bidirectional link is not required for printing or to have limited status feedback from the printer. However, unlike PCL printers, which can accept either PCL data wrapped in MLC or raw PCL data, PPA printers can only interpret data wrapped in VLink and SCP. Thus, while MLC is an option that can be added when a bidirectional link exists, VLink must handle printing with and without a bidirectional link as well as printing to a file.

Based on VLink's channelization features, there are two paths the data can take to the printer. One is for image data (the dots that will go on the page), and the other is for command data. Command data includes commands sent to the printer, such as "Print this sweep," requests for information, or queries, such as "What print cartridges are installed?", and status information, termed *autostatus*, such as "The top cover is open." Sending image data is easy from an I/O standpoint—if the printer has room in its buffer, the driver will send the data. Since command data must be sent and also received (autostatus may come in at any time), it is by nature a more complex affair.

As shown in Fig. 11, data that comes in from the front end of the driver goes through the data encapsulator, like PCL printer drivers, but from there it goes through several new objects. The SCP manager wraps the data in SCP and sends it to the I/O manager, which provides an interface to the datacomm objects. The VLink layer wraps the data in the VLink protocol and sends it to the IEEE 1284 layer and out to the printer. Data that is sent by the printer, such as notifications that something is wrong, are put in the printer's output buffer. The driver spawns a hidden executable at the beginning of each print job called the *port sniffer*, which checks the port every half second to determine if the printer has sent any data. If so, the data is routed through the IEEE 1284 layer to the VLink layer, which then posts a message to the I/O manager's hidden status window.

The status window uses a callback to call into the SCP manager, which translates the status information, and if the message is something that should be displayed to the user, puts it on the event list. The event list prioritizes the messages on it so that the most important message gets sent to the HP Toolbox, which displays the dialog box to the user. If the message is an error, it may get resolved (for example, the user puts paper in the printer and presses the **Resume** button). The message is then routed up through the same path and deleted from the event list. The Toolbox takes the dialog box down and displays the next most important message, if there is one.

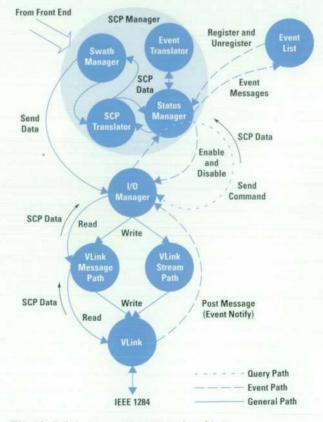

#### Internal Objects in PPA Status Messaging

PPA status messaging involves several high-level modules and objects: the SCP (Sleek Command Protocol) manager, the I/O manager, the VLink module, and the event list (see Fig. 12).

**SCP Translator.** The function of the SCP translator object in the SCP manager is to encode data into the SCP format and decode messages received in the SCP format from the printer into query replies and event information. The SCP translator

Fig. 12. Calls between status messaging objects.

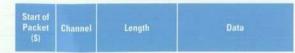

#### Fig. 13. SCP command format.

does not send SCP data directly to the I/O manager, since memory management for the data buffers is done in the SCP translator's clients, which are the swath manager and the status manager. The client of the SCP translator passes in a pointer to the data, an empty buffer, and the maximum data length. Once the data has been packaged, if the SCP translator finds that the data is larger than the buffer, it will return an error. Otherwise, it will pass back the actual SCP data length. The goal in designing the SCP translator was to encapsulate the Sleek Command Protocol so that changes in SCP in the firmware affect clients of this module as little as possible.

Commands in SCP use the format shown in Fig. 13. The command specifier field identifies the SCP command. The length field indicates the number of bytes in the data field. The data field does not exist for every command.

**Priorities.** Priorities allow the printer to execute commands in a different order than received. This may be necessary when a command cannot complete execution and it is desirable for the printer to process queries so the driver can find out what the problem is. Priority levels are defined in the SCP translator and the clients can set whatever priorities they like. Standard priority levels are defined as shown in Table I.

| Table I                                         |          |  |

|-------------------------------------------------|----------|--|

| Command Prio                                    | rities   |  |

| Command                                         | Priority |  |

| Printing Commands                               | Low      |  |

| Queries                                         | Medium   |  |

| Initializing and Deinitializing<br>the I/O Link | High     |  |

| Recovering from Errors                          | Recover  |  |

| Canceling                                       | Cancel   |  |

| Restarting the Printer                          | Restart  |  |

It is assumed that the swath manager will send all of its printing commands (LOAD\_MEDIA, PRINT\_SWEEP, EJECT\_MEDIA) at the lowest priority. Any queries it needs to make will call into the status manager. All queries should be at the same priority and higher than printing commands. It is up to the clients to set priorities.

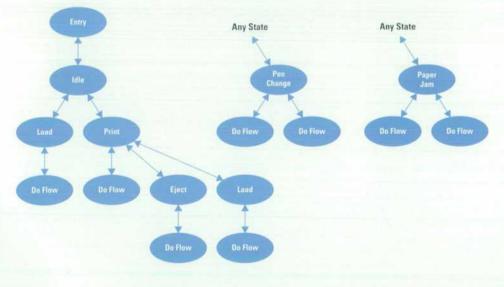

**Status Manager**. The status manager manages messages to and from the printer. These messages can be broken into two categories: events and queries. Events are unsolicited notifications by the printer (i.e., autostatus) that something has occurred to change the state of the printer, such as "the door is open." Queries are requests for information made by the driver to the printer, such as the pen IDs of the installed pens. The status manager tracks the state of the printer and creates events when state changes occur. For example, when the **Resume** button is pressed, an internal state change occurs. This state change is recognized by the status manager and reported as an event to the event translator.

When the status manager receives notification of an event, it determines what has changed and whether the event is something the event translator has requested to know about. If it is, a callback in the event translator is called.

Upon starting a print job, the status manager queries the printer to get the current state of events. No event notification will be received until an event occurs in the printer.

**Event Translator.** This module exists between the event list, which is Windows-specific, and the status manager. The event translator translates the bit-field data, which is returned to the status manager by the printer in autostatus, into events. New events are added to the event list by the status manager, and events that are no longer valid (e.g., the door was open but the user shut it) are removed from the list. The event list orders the events reported to it according to their importance to the user, and tells the status monitor which dialog box to display. From most important (1) to least important (10), the following event priorities are used: (1) I/O errors, (2) paper jam, carriage stall, or maximum thermal limit, (3) pen failure, (4) wrong pen, (5) low or out of ink, (6) pen missing, (7) out of paper, (8) cover open, (9) dry timer, (10) new pen.

**I/O Manager**. This module is intended to glue the VLink module, which is Windows-specific, to the SCP manager, which is shared. Handling for events, queries, and buffer management must be performed by the I/O manager in addition to sending data to the printer as quickly as possible.

**Events.** The I/O manager creates a hidden window so that when the printer sends unsolicited event notification, Windows messages to that effect can be posted to this window by the VLink module. When the I/O manager processes this window message, it will read the SCP data buffered by VLink and call a callback in the status manager, passing in the SCP data.

**Queries.** To get replies to queries, the inquiring module calls VLink, specifying a buffer in which to place the reply. VLink checks this query reply buffer to see if anything has been returned in response to the query. If so, it immediately returns with the SCP data. If not, it polls the incoming channels for a specified timeout period to attempt to retrieve the reply. If a reply is received before the timeout period expires, the SCP data is passed through to the status manager.

**Datacomm Paths.** The image and command datacomm paths send data to the printer as long as there is space in the buffer. If space runs out, the command datacomm path waits until more space becomes available. The image data is handled differently. If space runs out while sending image data, the image datacomm path returns to the caller, allowing it to render more swaths until more space becomes free in the printer.

VLink. The VLink module must package data in a protocol the printer recognizes, and send only as much data as the printer can take, as quickly as possible. VLink must also unwrap data from the printer and route the messages to the appropriate clients. The VLink protocol replaces MLC (Multiple Logical Channels) for the HP DeskJet 820C. Like MLC, VLink's intent is to provide a way for the host and the peripheral to exchange data. Unlike MLC, VLink is not optional. All data going to the printer must be wrapped in its protocol. In addition, VLink is streamlined or "sleek," and doesn't have many of MLC's features. MLC supported multiple logical channels, while VLink supports two outgoing and three incoming channels.

**Outgoing Channels.** The printer accepts data in either its input buffer or its command buffer. The VLink module specifies which type of data it is sending through a field in the VLink packet header. A template of a VLink packet is shown in Fig. 14.

Image data is sent to the printer's input buffer on the image data output channel. Commands and queries are sent to the command buffer on the command data output channel.

**Incoming Channels.** Since a bidirectional link cannot be guaranteed, all incoming data is optional. This is necessary for file dumps and bad cables, and miscellaneous communication problems.

The printer periodically notifies the host how much buffer space is left in the printer. This is known as *credit*, and the printer sends notification for both the command and input buffers on the credit input channel. The VLink module will not send more data than the available credit.

VLink accepts two types of data packets from the printer in addition to credit packets: query replies, which are expected on the status input channel, and a collection of bundled items regarding printer status (such as out of paper), called autostatus messages. Autostatus messages ultimately map to events.

An autostatus message from the printer consists of a bit collection of several long words representing the current state of the printer. For example, when the door is opened, the door open bit in the collection is set to true. A report is generated on the autostatus input channel when any of these bits are toggled.

When the VLink layer receives some data, the data is identified as either credit, a query reply, or an autostatus message. Credit is interpreted and handled within the VLink module. A query reply or an autostatus message is buffered internally so that the clients can read it later.

If a received message is an autostatus message, the VLink layer posts a Windows message to the I/O manager indicating that an autostatus message is waiting to be read. When the I/O manager processes the Windows message, it reads the buffered autostatus message. Posting a message is necessary so that VLink can be free to poll the data lines for more incoming data from the printer.

Once the buffered message has been read, it is deleted. Only one query reply and one autostatus message can be buffered at a time. If a new message comes in before the original

Fig. 14. VLink packet format.

message can be read, the new message replaces the old one. It is for this reason that no additional printer queries should be made while waiting for a reply. No harm is done if a new autostatus message overwrites the old message because the same information is contained in each message and the newest message is the most relevant.

#### PCL Emulation for DOS Application Support

The development period of the HP DeskJet 820C coincided with most users rapidly transitioning away from DOS applications towards Windows applications. While we expected that most users would use the printer in its optimized design center, we recognized that we needed an adequate bridge to the few DOS applications that would continue to be used.

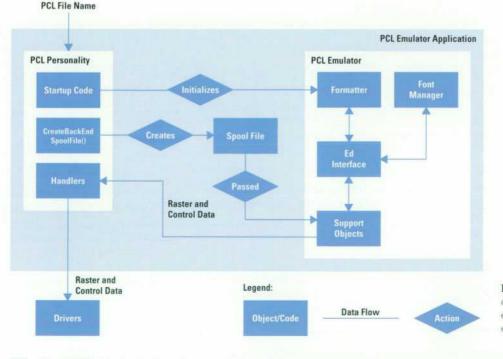

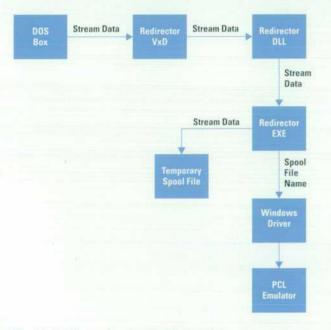

The HP DeskJet 550C printer was the final printer to be supported by most DOS applications, so the solution had to be functionally compatible with this printer and provide equally good print quality. We chose to provide compatibility with the HP DeskJet 660C printer, which was a contemporary printer that satisfied these requirements and provided an internal interface that enabled us to separate the PCL personality from the printer engine firmware. We planned to port the PCL personality functions to the HP DeskJet 820C printer driver, encapsulating them in a PCL emulator module. The required printer-engine functions would then be supplied by the rest of the HP DeskJet 820C driver. In this way, we could minimize design changes and maximize the chances of identical compatibility. If a DOS application is run from an MS-DOS prompt window, also referred to as a DOS box, the printer driver can intercept the PCL data stream that the DOS application sends to the PC's parallel port and redirect the data stream to the PCL emulator.

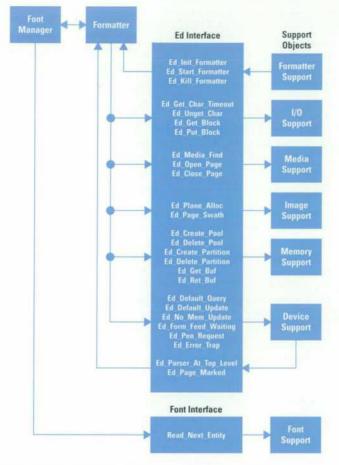

The HP DeskJet 820C PCL emulator encapsulates the HP DeskJet 660C formatter and text engine code. The design of the HP DeskJet 660C firmware was such that all interfacing to the external mechanism was done through a well-defined API internally known as the *Ed Interface* (see Fig. 15).

The Ed Interface resides between the formatter and font manager and the rest of the firmware. It is a collection of function calls to the support code in the firmware. Since we reused the formatter and font manager code, we provided the equivalent firmware functionality by mapping the Ed Interface calls into HP DeskJet 820C support objects.

The functions of the formatter and text engine firmware code were written in C, and as such are functions in the PCL emulator application (Fig. 16). The PCL emulator application provides C++ objects that encapsulate the functionality expected by the Ed Interface.